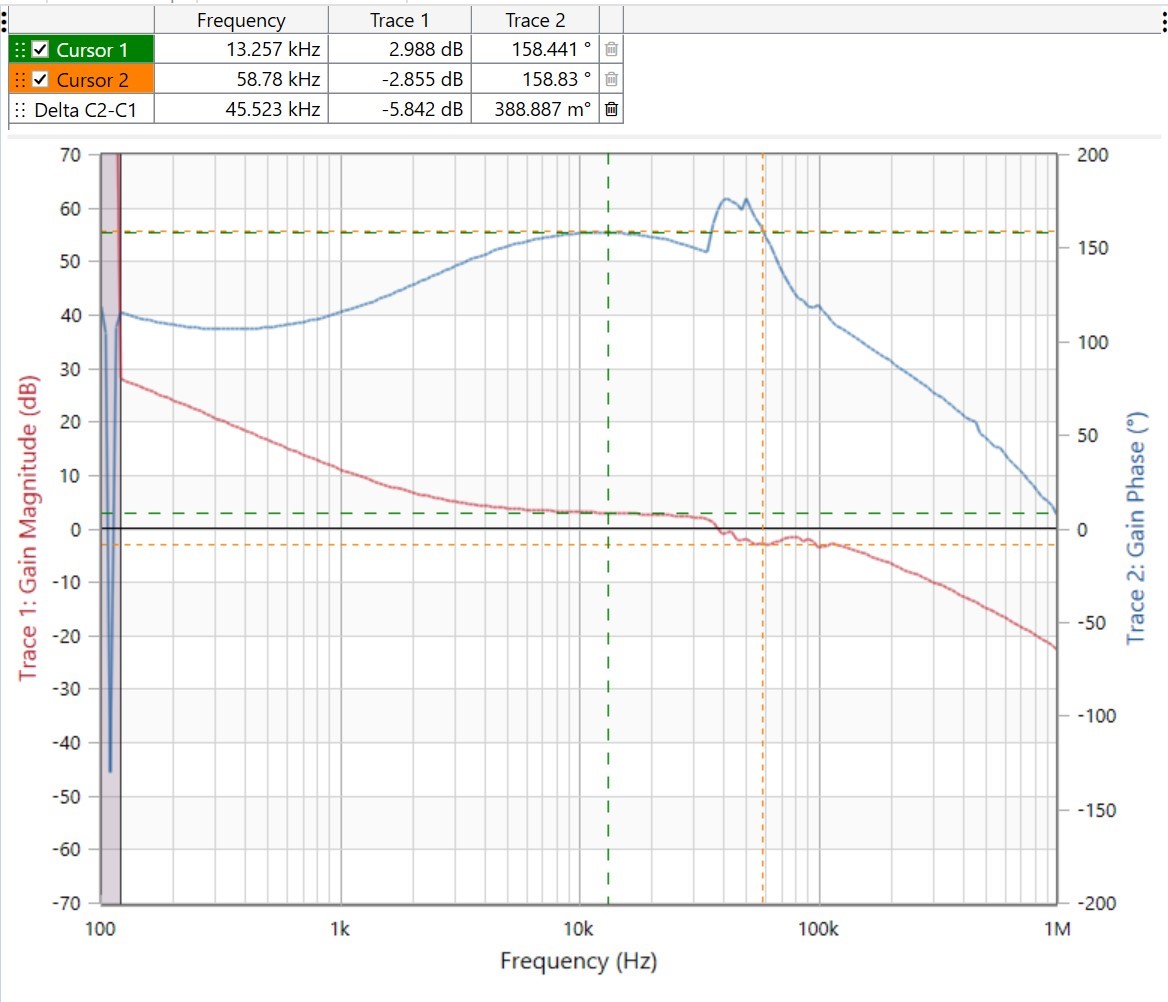

What is the Unity Gain Bandwidth of the internal error amplifiers for this device? The data sheet does not specify. and I suspect we might be BW limiting with higher Rcomp values.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.