Other Parts Discussed in Thread: TPS7A02, TPS63806EVM, TPS63806

Hi Team,

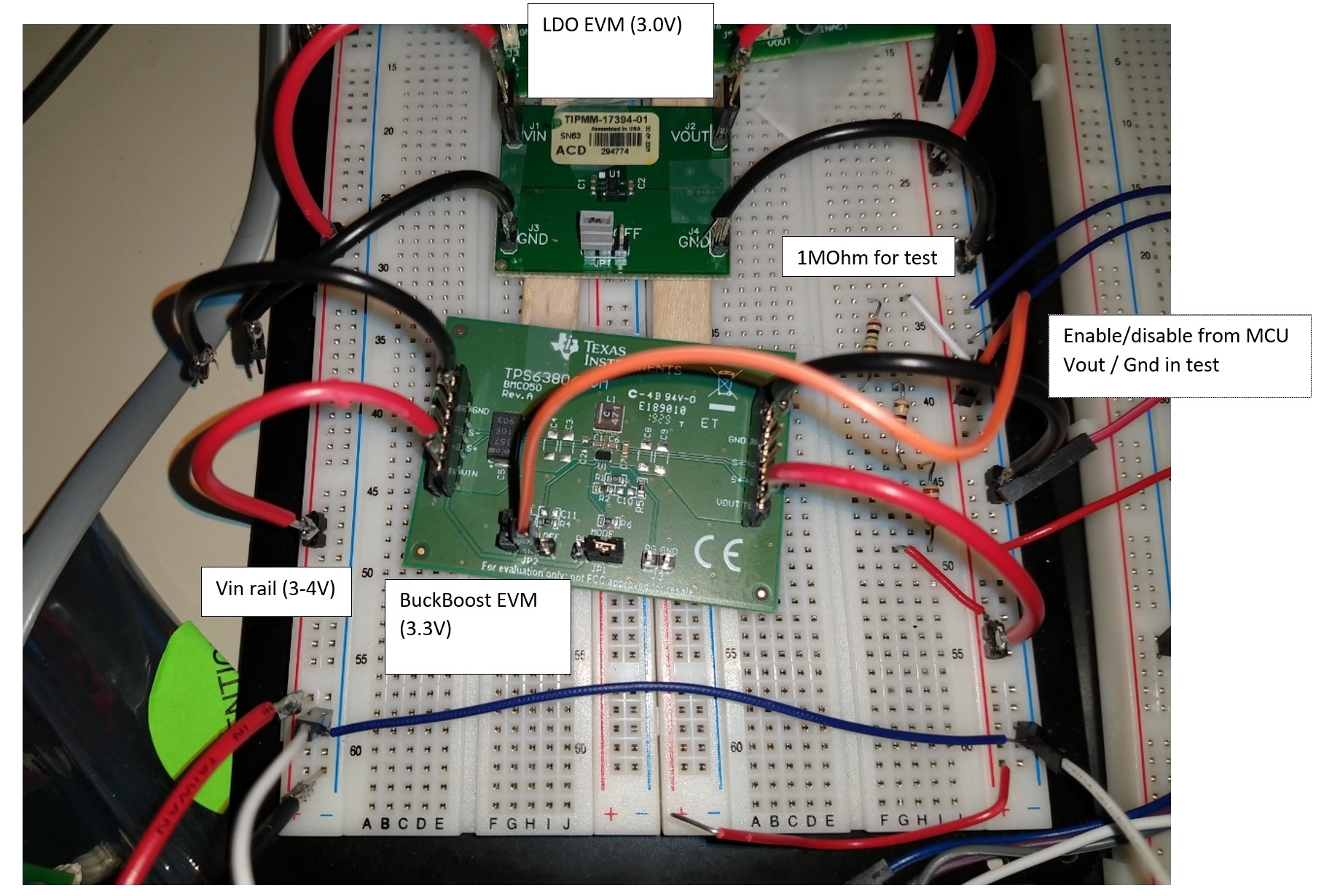

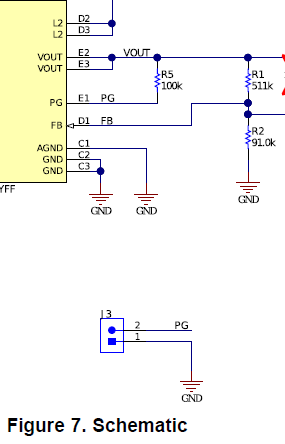

Need your inputs on this. Our customer is using an MCU to control a battery charger. On the field, as the the MCU goes standby mode it would need to consume 3.3V at very low currents all the time. This would make the current DC/DC converter (MCU supply) to consume more than the sleeping MCU.

The TPS782 would perform much better when the controller is in deep or light sleep and when most of the system is powered down. This would enable the controller to wake up when needed and then activate the converter to come online before loading up with more current.

Do we have any suggestions, app notes or design documents to manage this handover between the LDO and switching converter? Thanks in advance!

Kind Regards,

Jejomar