Other Parts Discussed in Thread: TPS53915, TPS53317A, TPS53317

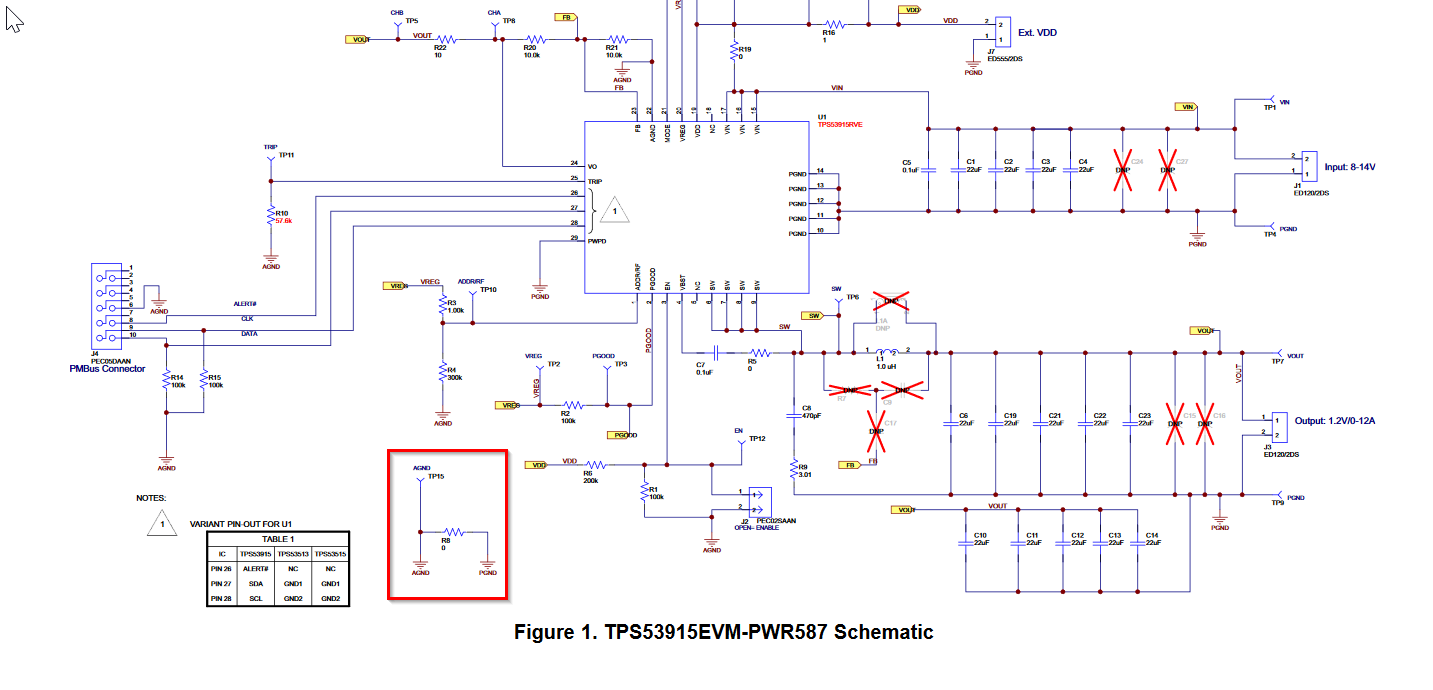

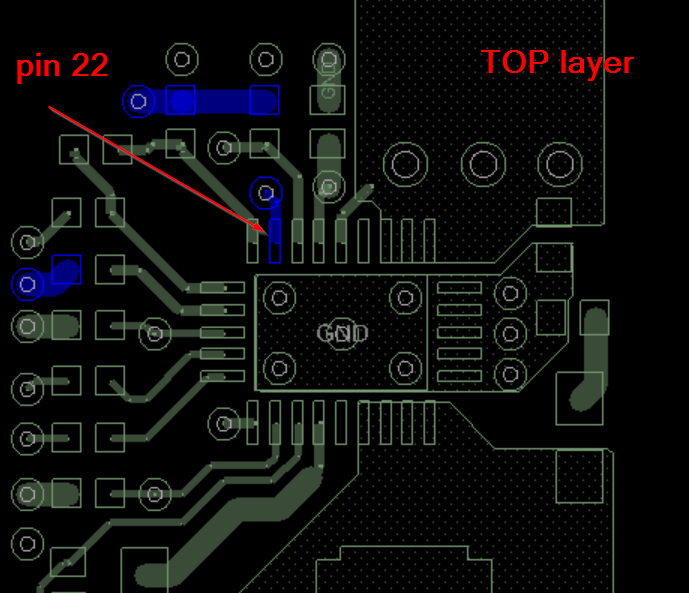

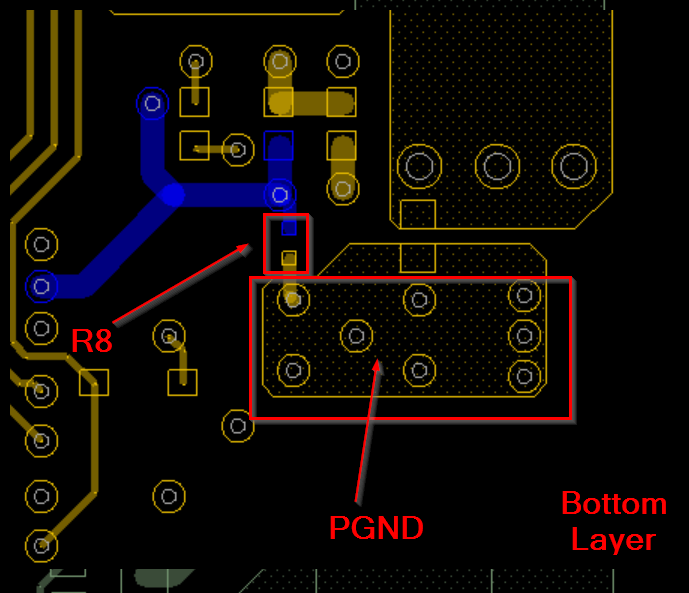

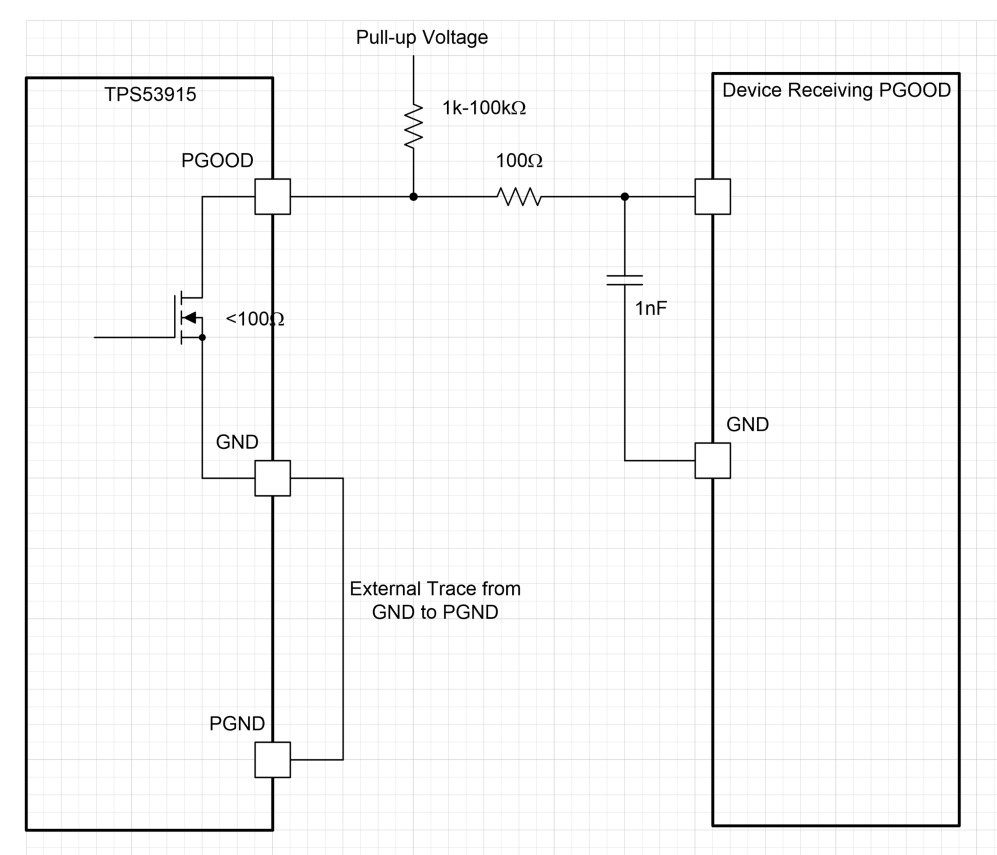

Q1) I found that in the schematic is AGND (pin 22) connected to PGND via resistor R8 = 0R but in the top layer, I saw that pin 22 (AGND) connected directly to IC's Thermal Pad. So that I get confused about this connection. Which one is correct?

Q2) Can R8 change be to ferrite bead? and Can you recommend the part number?

I also attached the picture for more details.

Thanks a lot