Other Parts Discussed in Thread: BQ76920

Dear Forum Members,

I have a BQ77915EVM card and try to test it in 3 cell configuration with real Li-ion cells.

I successfully tested the Discharge Overcurrent (OCD), Short (SCD), Undervoltage (UV) protections with oscilloscope (CH1: current sensing resistor signal, CH2: DFET Gate, with Single Mode) and

Normal/hibernating modes current consumptions (with DMM, they are fullfil the specifications, note, very attractive values).

Now I am checking balance operation but I met promblems: the balance procedure started but after expering certain amount of time it has stopped, thus the cells remained in unbalanced state.

I used mult-channel analog signal recorder for this test. I made two test: one did utilize only minor initial unbalanced condition, second used larger (allowing to raise OV event-> CFET turned off).

Charger setup. CCCV by PSU: 1A, 12,3V (3*4,1V, because '77915-00 variant has OVD=4,200V, Vfc=4,100V). Jumper in CBI state on EVM.

Somebody could suggest idea why stopped the balancing? Unfortunately the datasheet does not detail the stop conddition neither Vcbth nor Vcbtl (abs) levels, only a 100mV hysteresis mentioned. From my experiments, it seems balance starts at 4,1V (pls see ath pictures).

Thanks in advance for the comments!

Joseph

Graphs: CH1 RED: Lowe cell, CH2 BLUE: Middle cell, CH3 GREEN: top cell, CH4 PURPLE: CFET Gate, CH5 Orange: signal on current sensing element. Note: channels 1-3 are connected to

RINs lower pad (IC VCx pins) thus when balance ON the measured voltage value corrupted...but it is not so important, I wanted to see how switching. When balance OFF: measured voltage values became again correct for the analyzer.

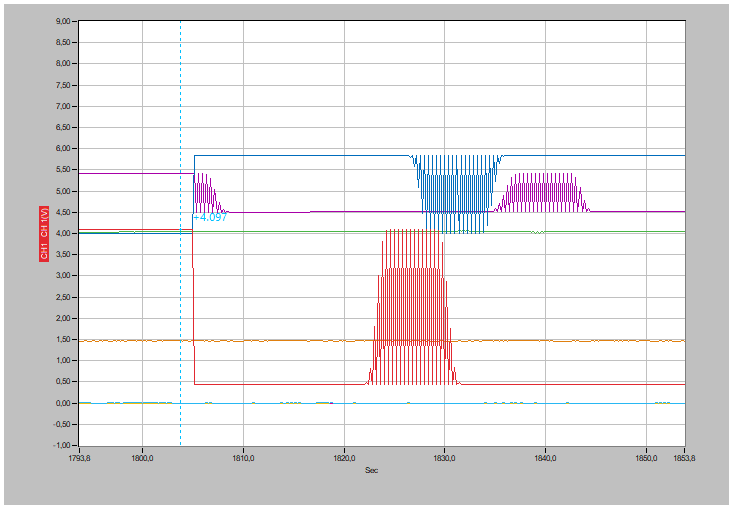

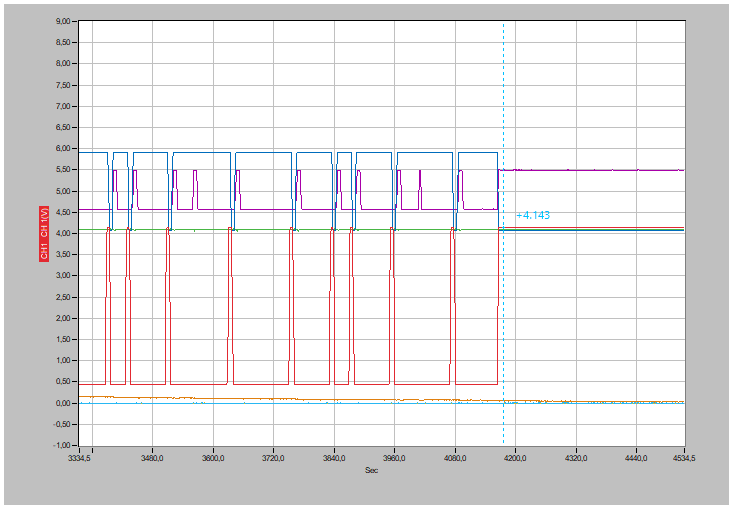

Minor initial unbalance, sample rate: 200msec (max speed). Before turing ON charger, cells are: 3,763, 3,703, 3,712V

Magnify : it is corresponding to datasheet which states the BQ applies 200ms balance-test interval

End: by the end cells: 4,143, 4,069, 4,093V

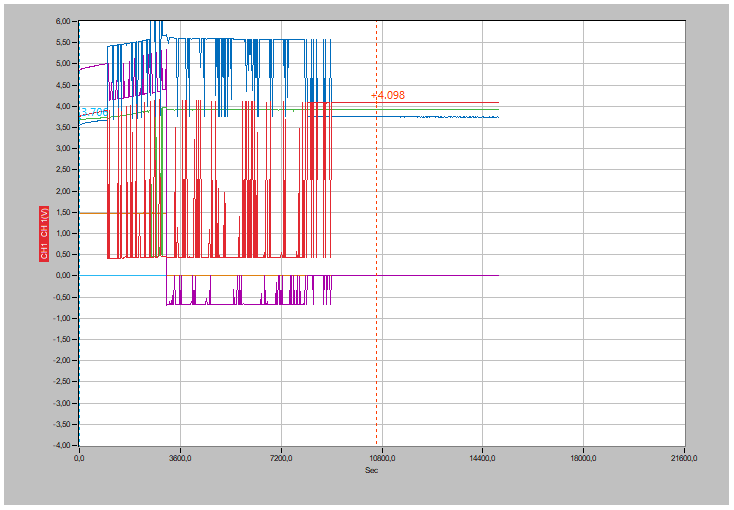

with Larger initial unbalance: cells: 3,706, 3,508, 3,620 before turning ON charger

It can be seen, CFET also turns OFF (top cell reached the OVD level)

By end of procedure: 4,098, 3,748, 3,921V thus highly unbalanced