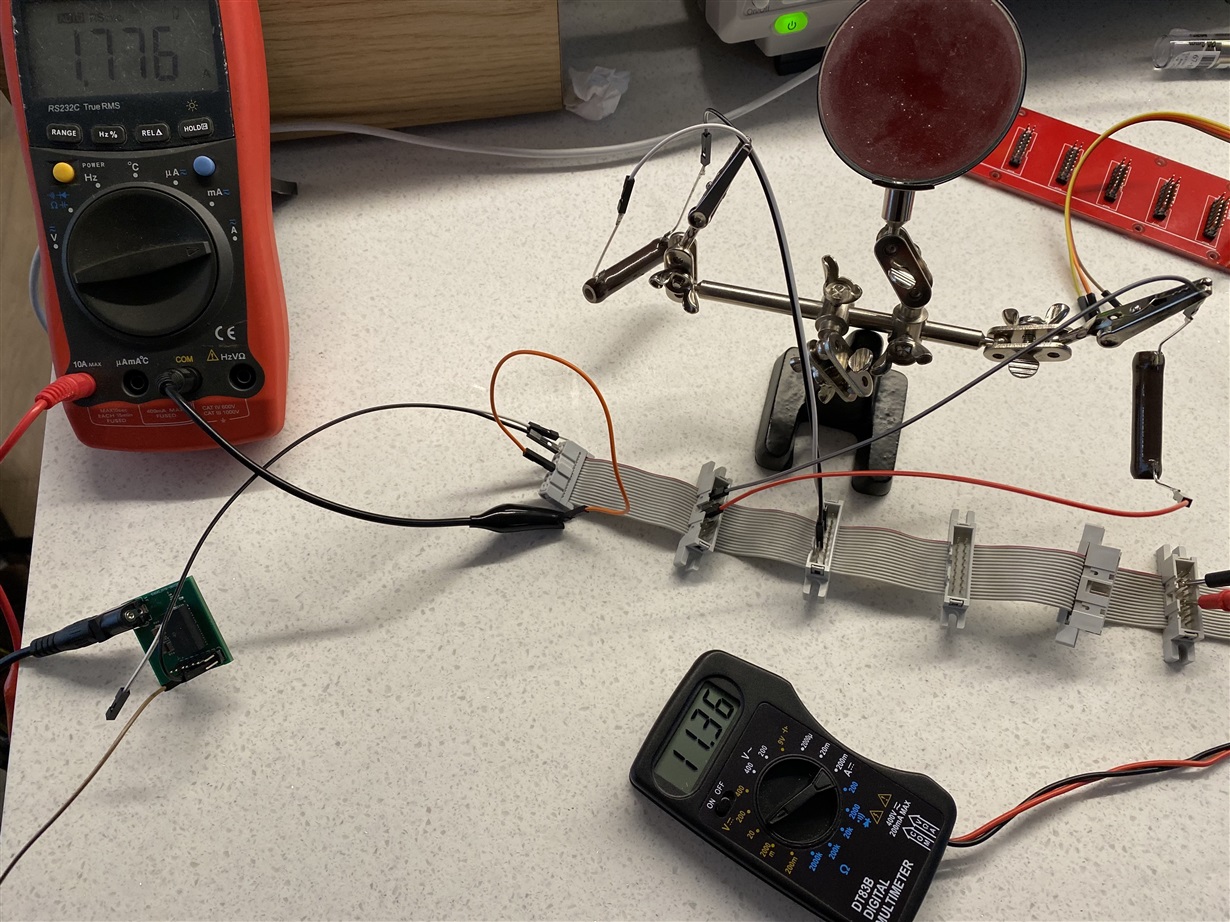

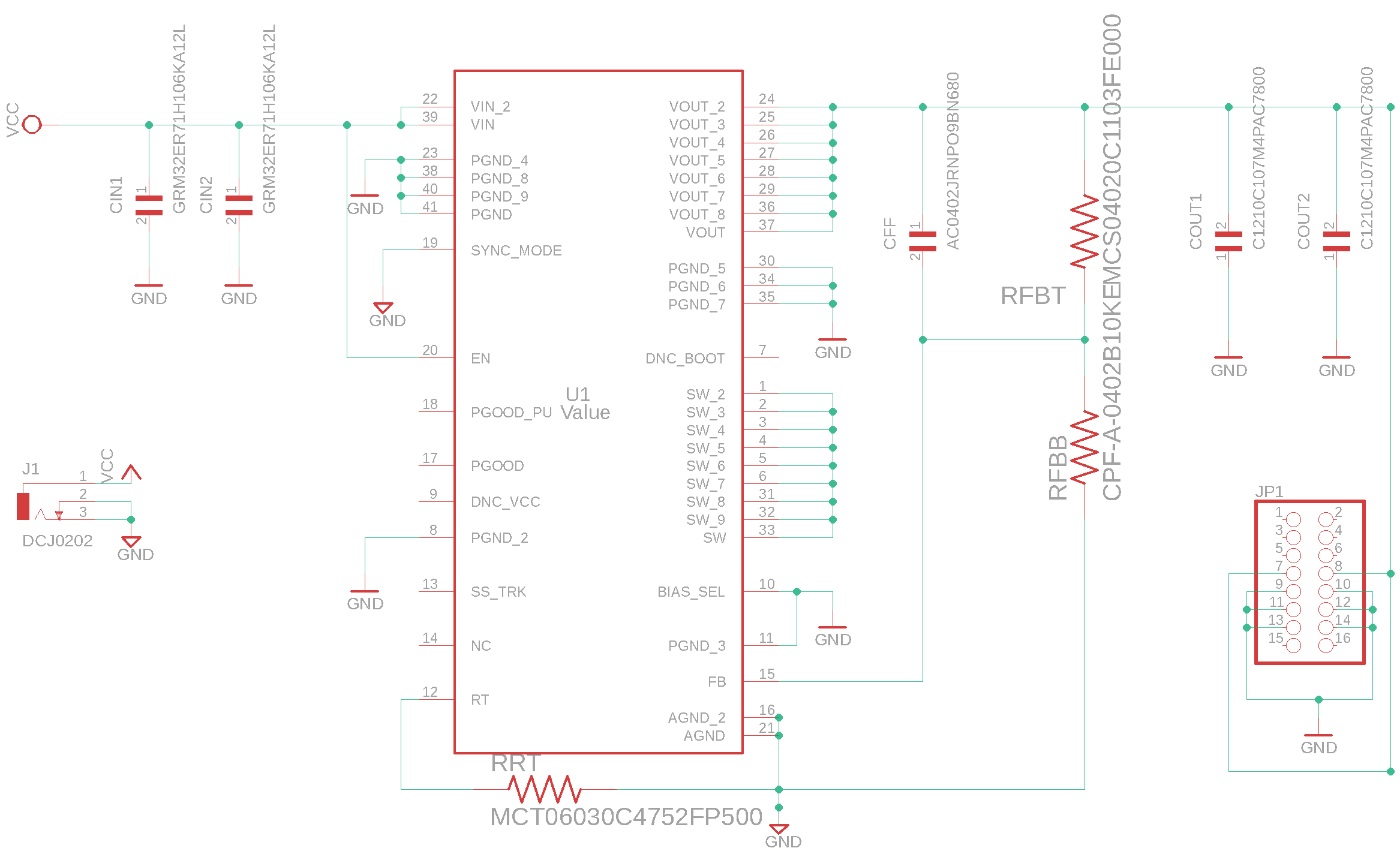

I have two 12 ohm resistors (rated 12w each) attached to a flying bus cable being powered by a board with the LMZM33606 chip. The current being drawn is 1.776 A. Using a multimeter to measure another port in the flying bus cable the voltage is only 11.36V and not the expected 12V. Please advise what is the reason for this drop in voltage and how it can be fixed. Thanks

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.