Dear expert,

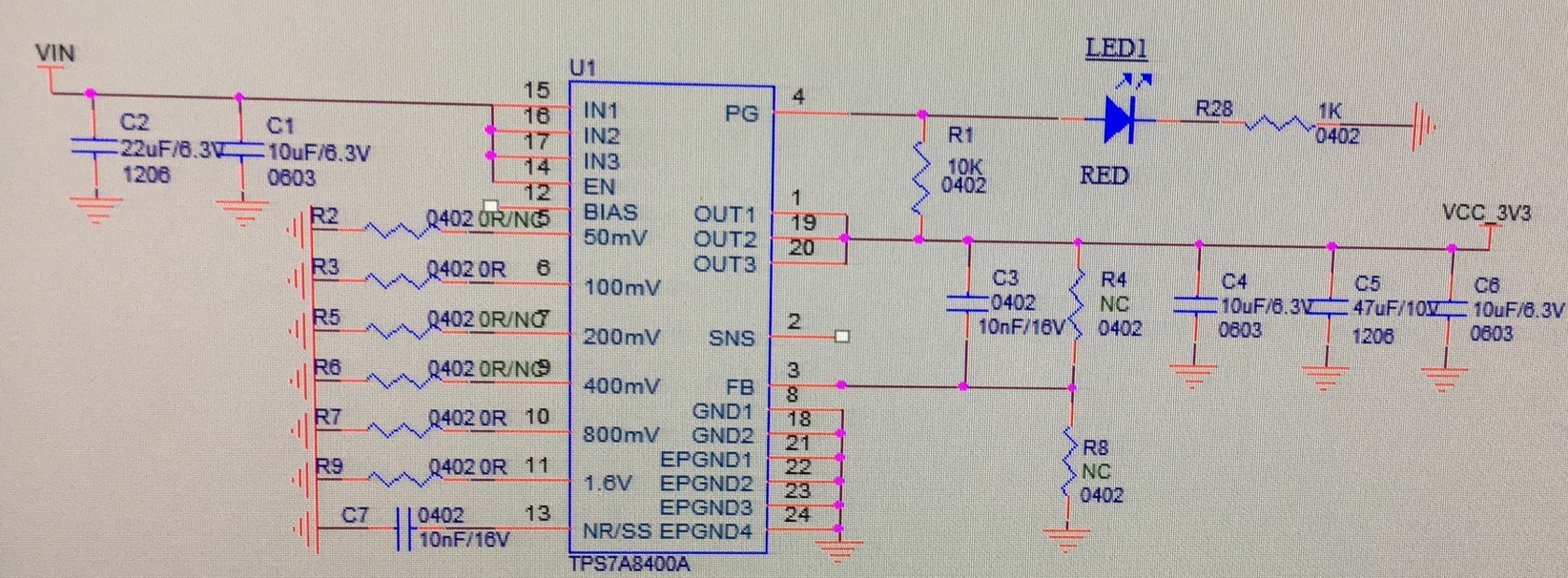

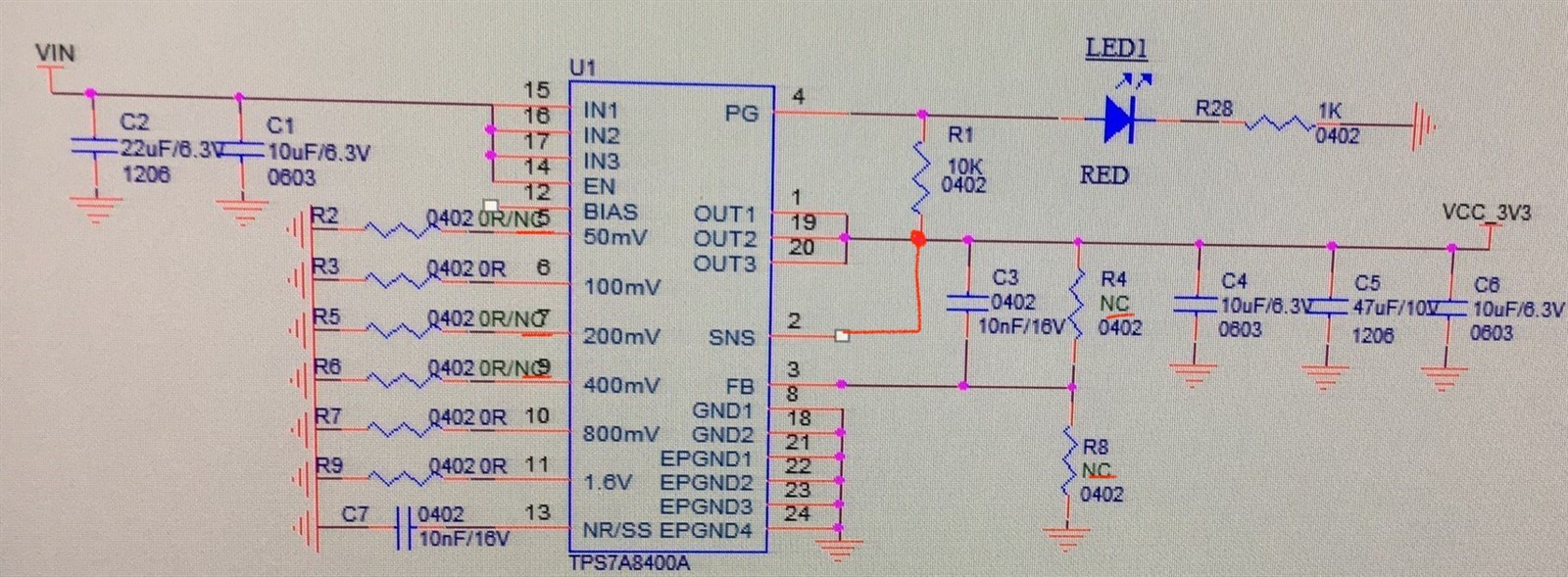

My customer is using TPS7A8400A to develop a low-noise, high-accuracy LDO, as shown in the figure. It is 3.3V ~ 5V input, 3.3V fixed voltage output, load current starts 2.5A, stable 0.9A.

There are also several uncertain issues:

1. Does the SNS pin need to be connected to OUT without modifying the resolution of the internal reference voltage?

2. If the input and output voltage is greater than 2.2V, is it beneficial to reduce the noise by connecting bias to the power supply pin?

3. Can the PG pin be connected to the LED light to indicate whether the circuit is faulty? Is there a problem if I connect as shown in this picture?

4. How to judge which one is used, the internal fixed voltage or the resistance voltage division on the FB pin?

5. In order to achieve the best effect of suppressing noise and high frequency, are there any improvement of the input and output filter capacitors and other bypass capacitors as shown in the figure?

Thanks for your support!