Other Parts Discussed in Thread: TPS51200

Hi

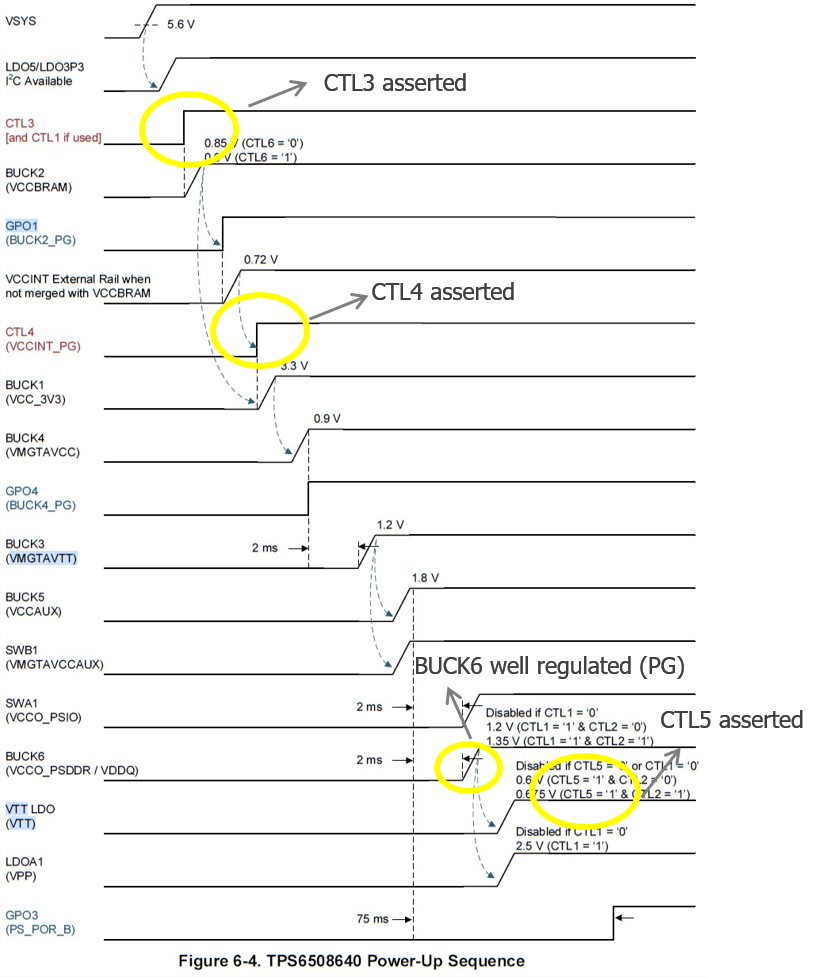

I'm referring datasheet of TPS650864, whose version is SWCS138C, and I have a question for Figure 6-3 TPS6508640 Power Map example.

It was not clear for me how to use GPO2 in Figure 6-3.

Could you tell me a role of GPO2 as I2C GPO in Figure 6-3.

BestRegards