Tool/software: WEBENCH® Design Tools

Hi,

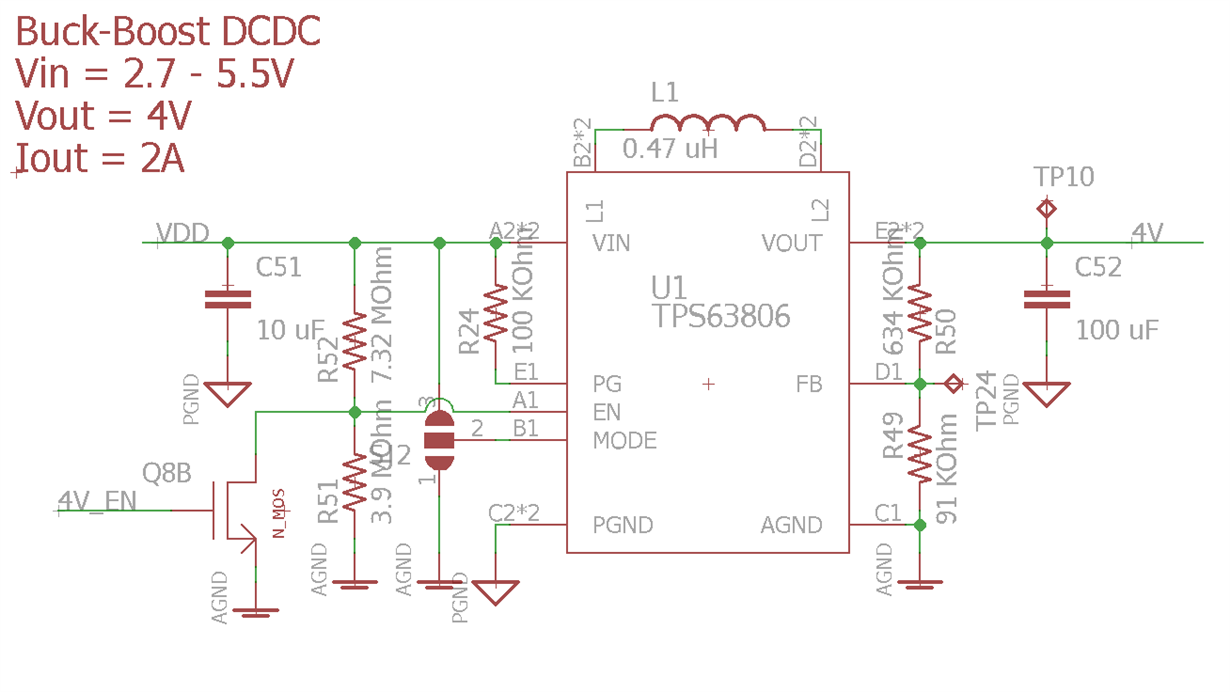

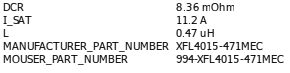

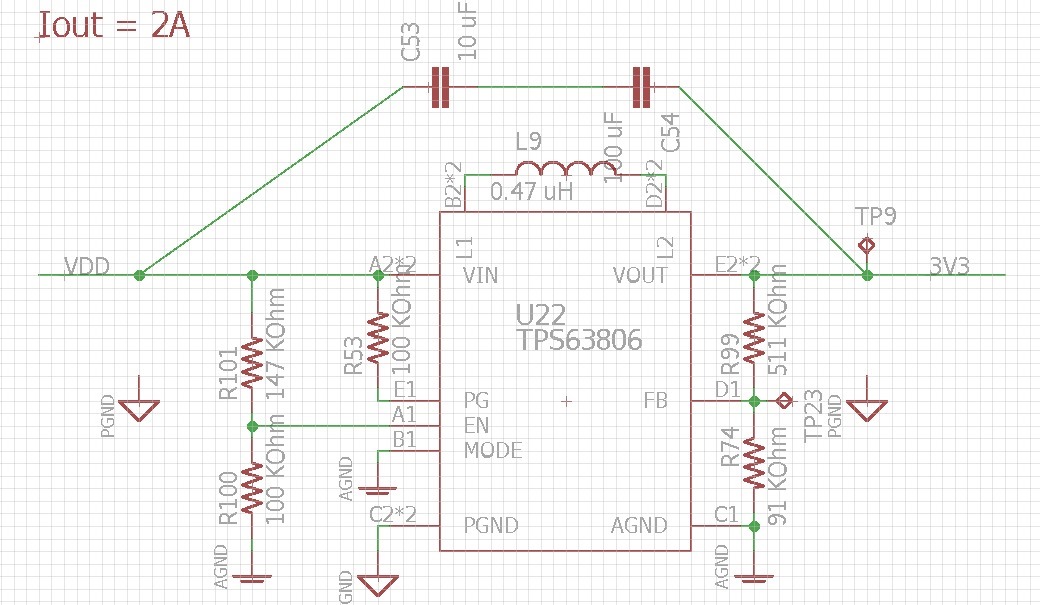

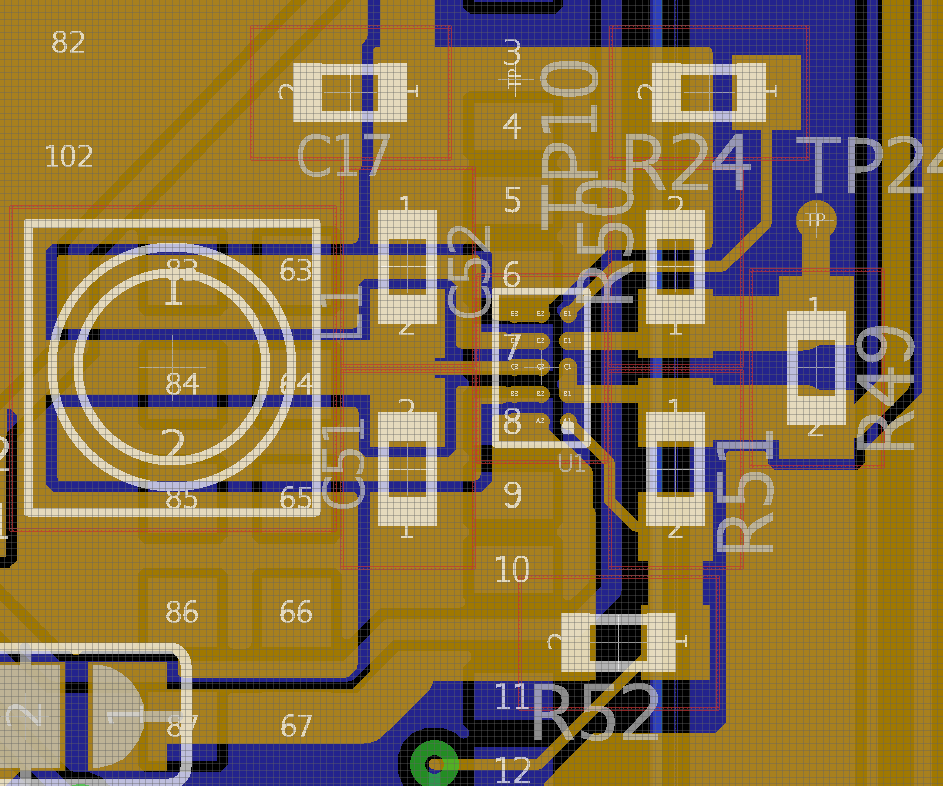

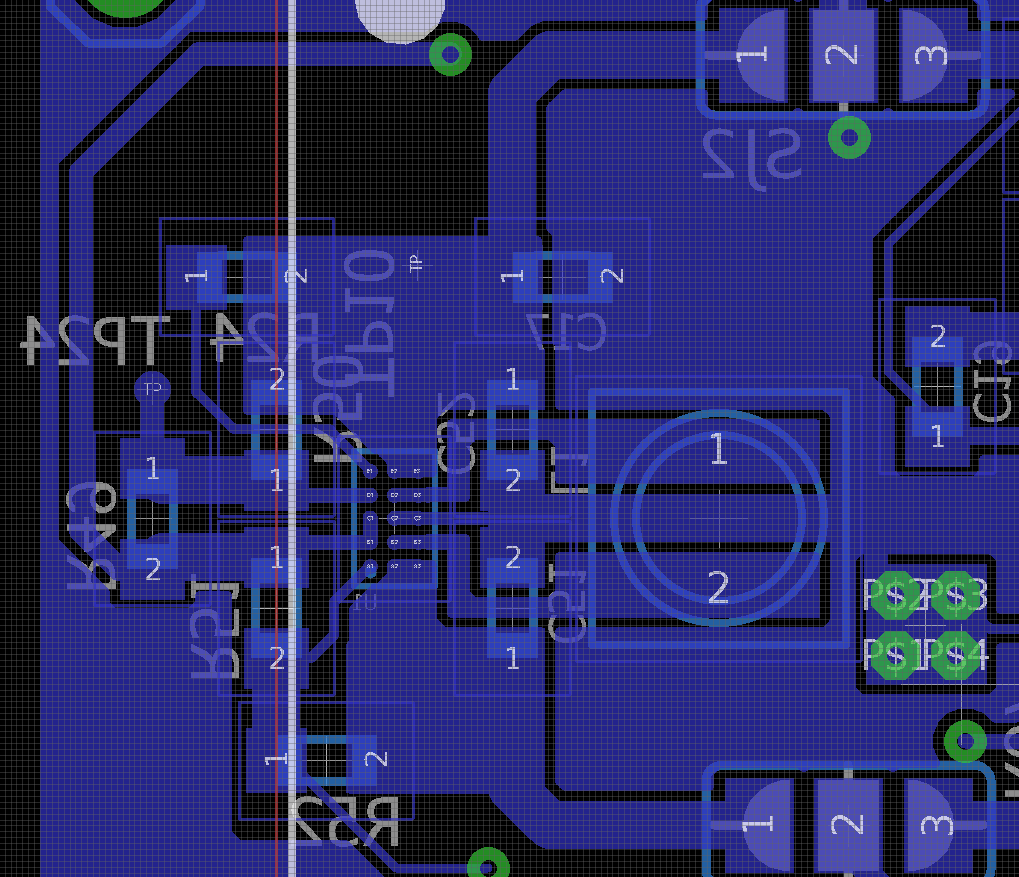

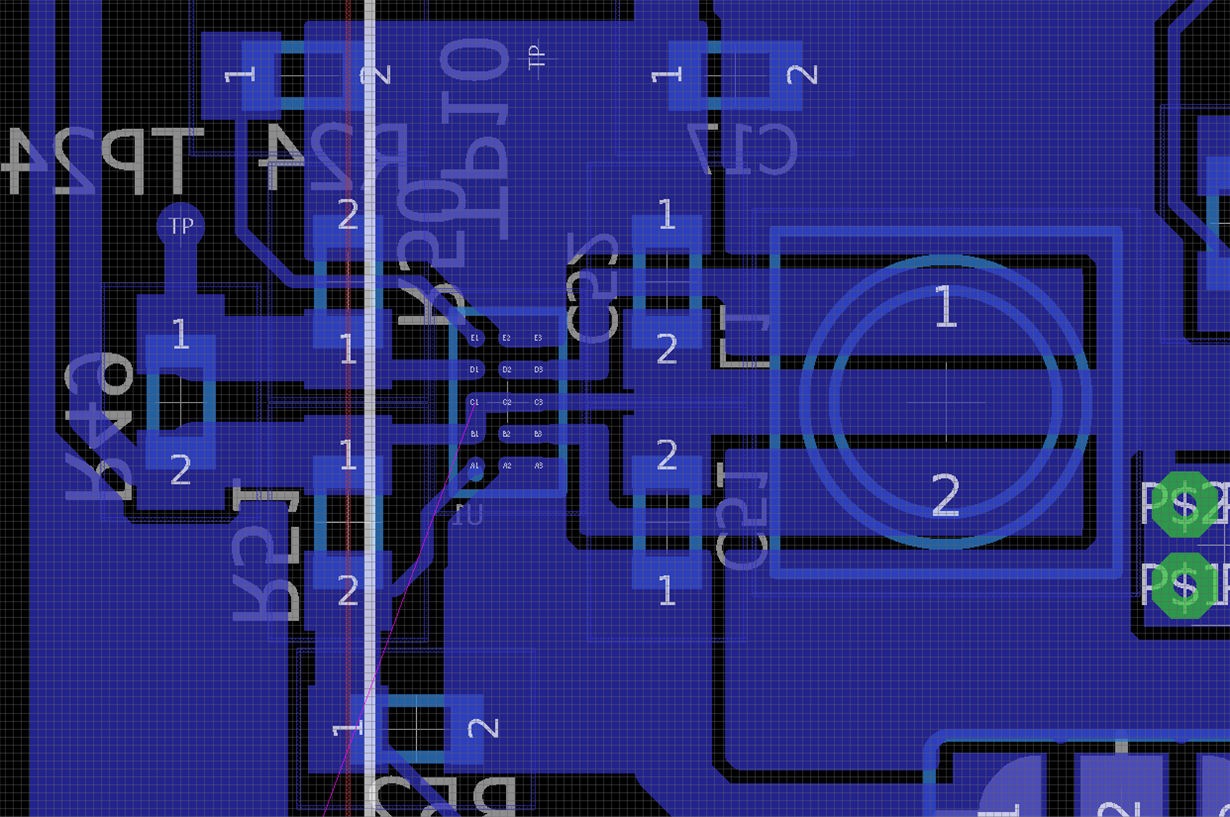

Next is the circuit I'm using to supply an IC with a 4V input and it can have some 2A peaks of consumption, designed with the WEBENCH tool:

The mode pin is connected to VDD (a 3.7 Li-Ion battery) so it should work in both PFM/PWM modes depending on the consumption.

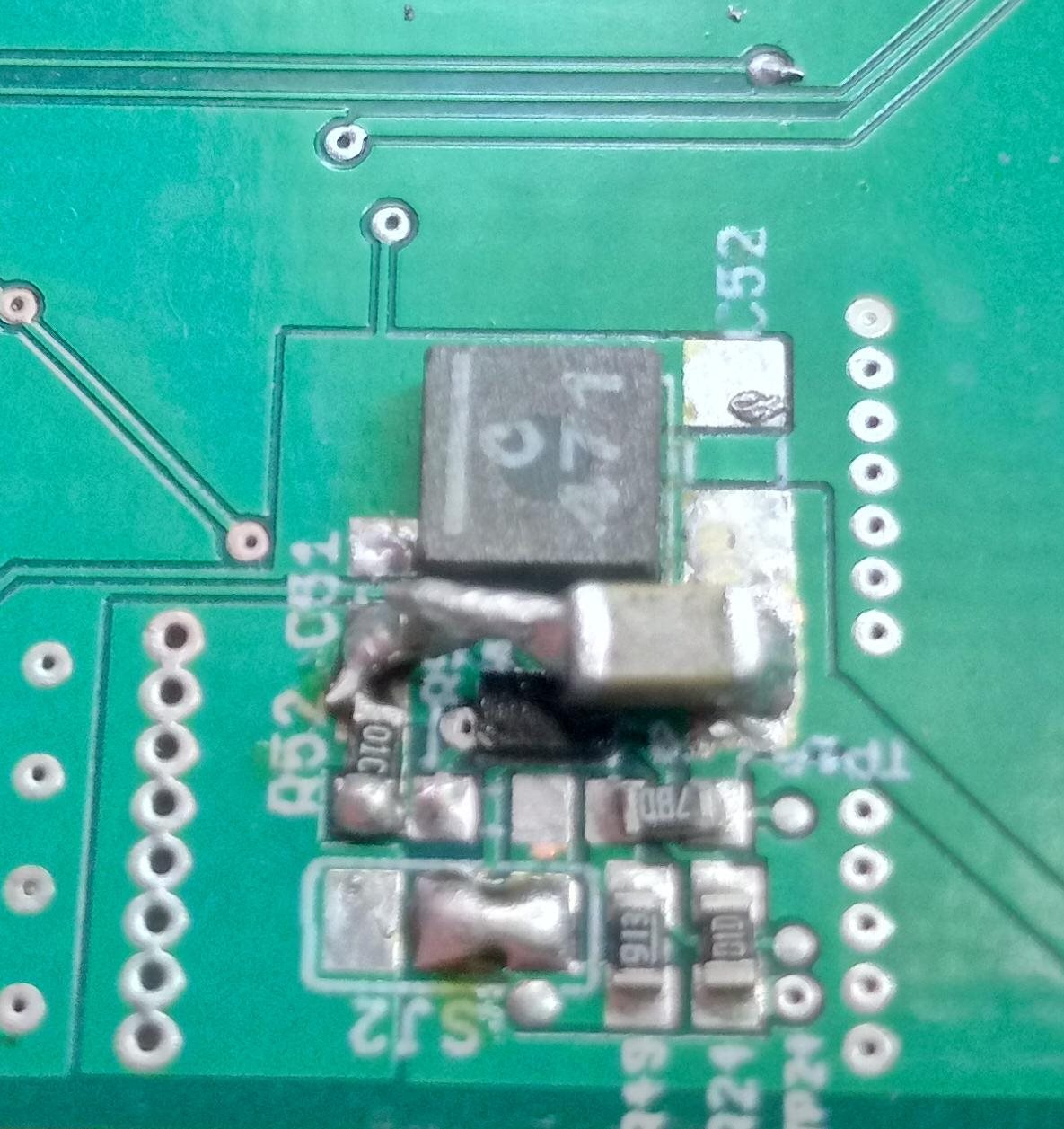

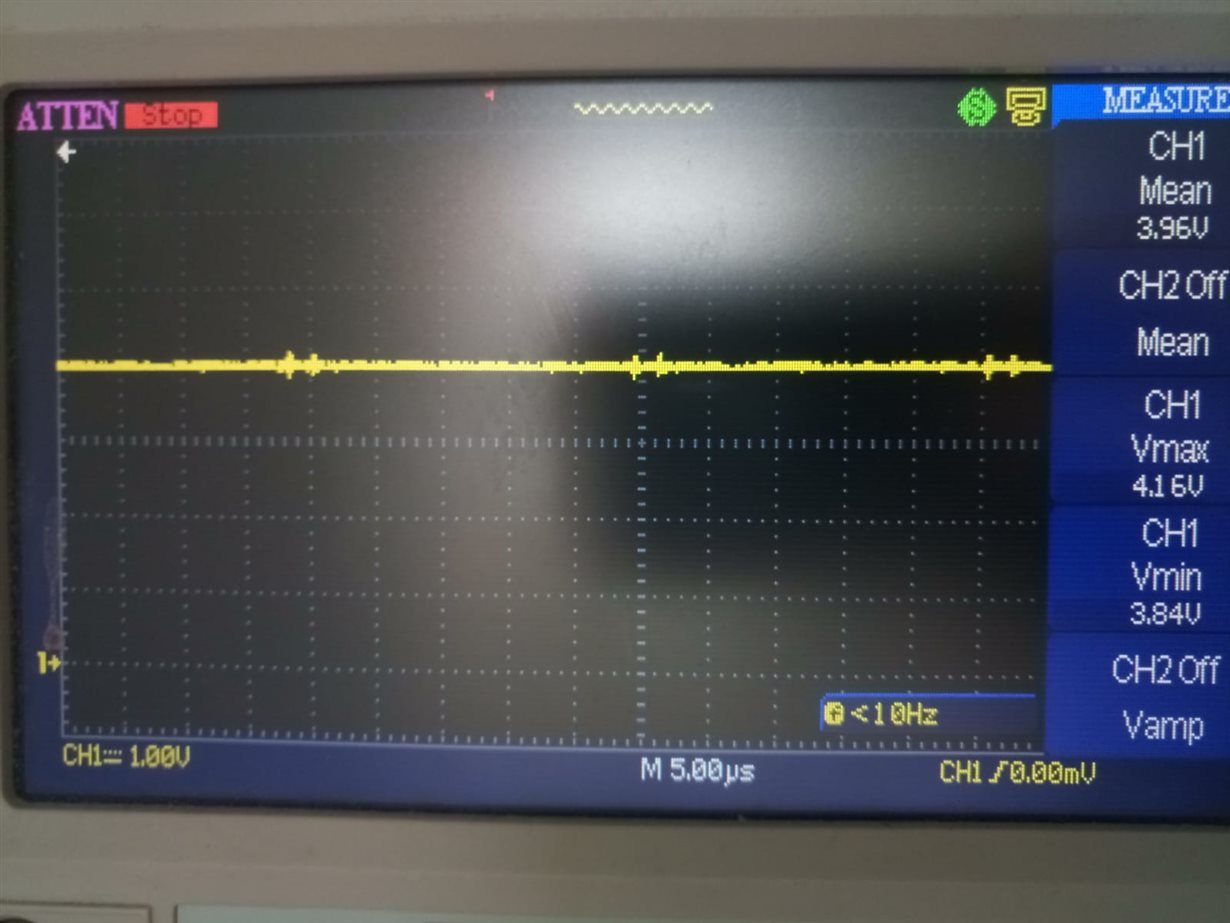

My problem is that without reason it starts to heat up, and altough it seems to stay at 3.8V (which is less than the desired voltage, yet useful for the IC) looks like it can't supply anything.

Also after a while it goes to some mV at the output (like a short circuit) with no reason.

The best explanation I thought it was some ESD thing, due to "touching" the TPS63806 but after burning some of them and being SUPER careful of not touching it still fail.

Any idea why?

Best regards,

P