Other Parts Discussed in Thread: LM5110

Hello seniors,

I modeled the 48V to 5V prototype based on the half-bridge circuit in the LM5035 manual. The circuit diagram is similar to the following figure:

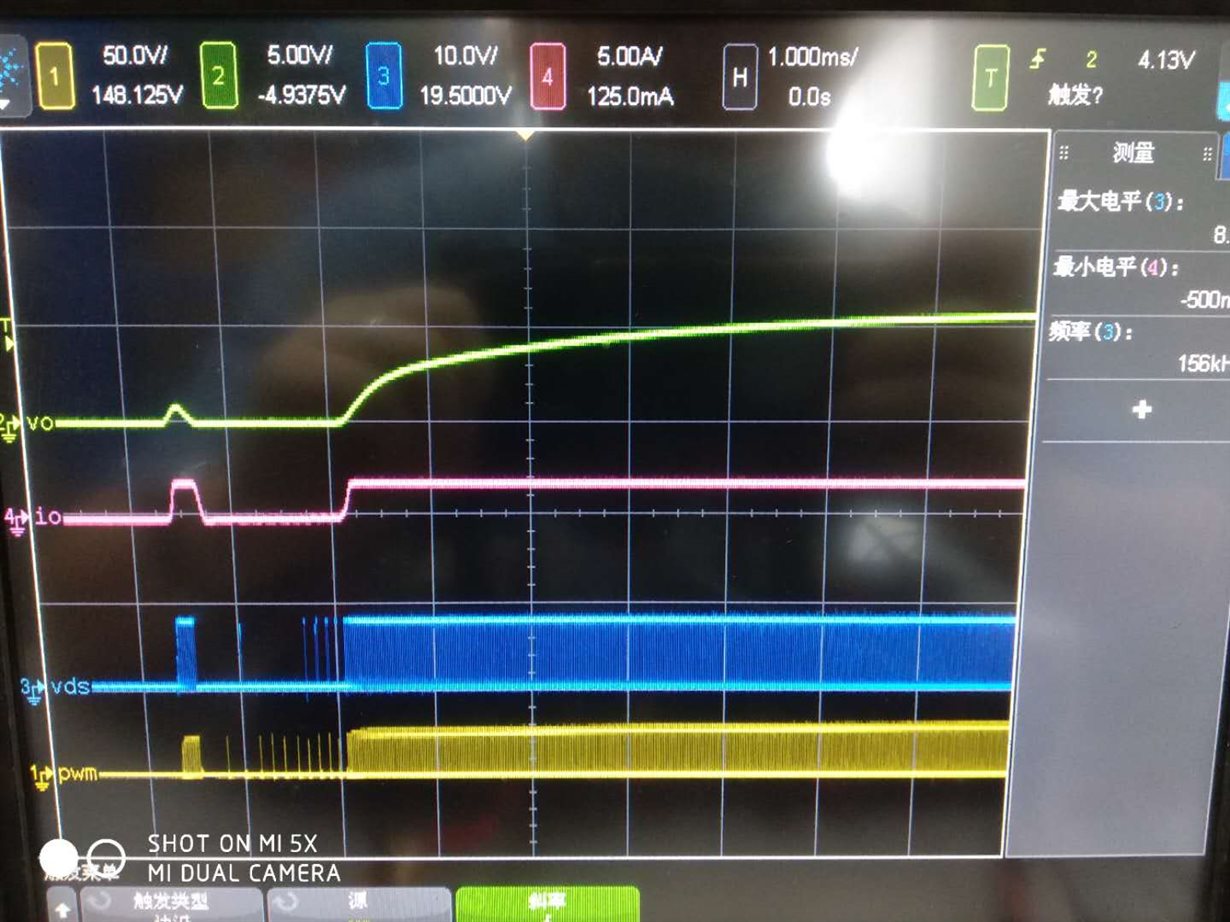

During commissioning, it is found that there is one abnormal phenomenon in the secondary synchronous rectification part at the moment of starting and shutting down. Please also give pointers.

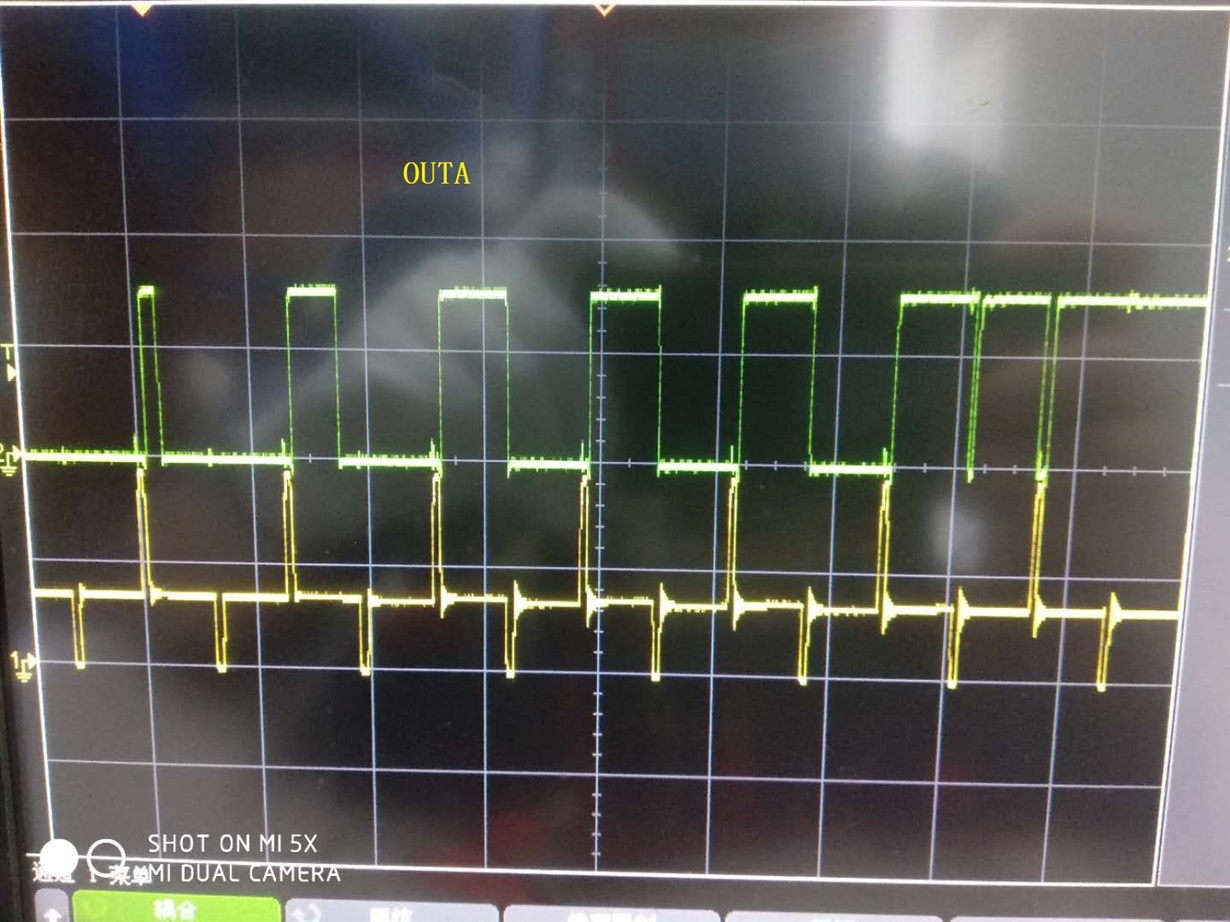

During startup, the output waveforms of OUTA and OUTB of the secondary synchronous rectifier driver U2 are different, as shown below:

As shown in the above two figures, OUTB gradually increases at the instant of no-load startup, and about 4 cycles are stable, while OUTA requires 6-7 cycles, and the shapes of the two are inconsistent. The yellow-colored PWM wave is the corresponding primary MOS tube driving wave.

Not sure why OUTA and OUTB are inconsistent?

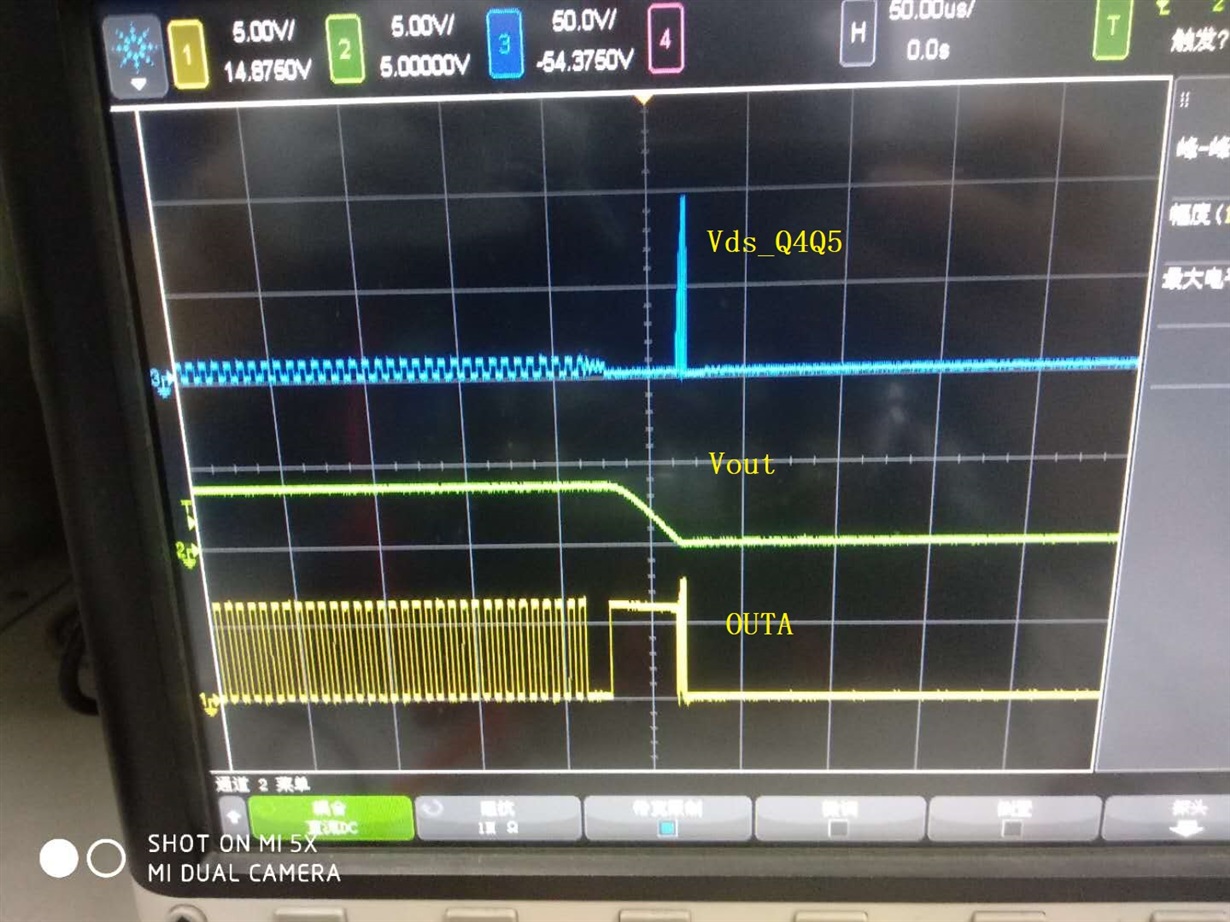

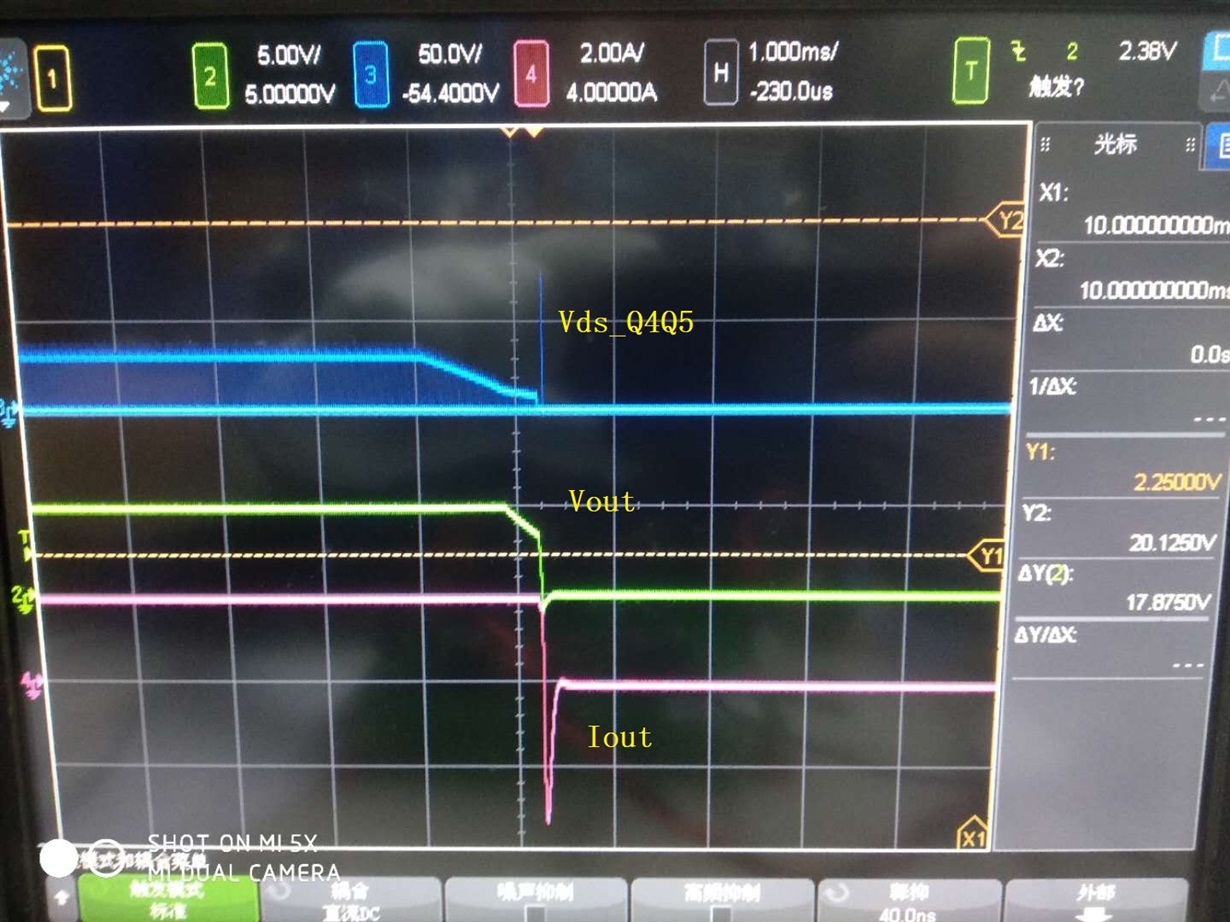

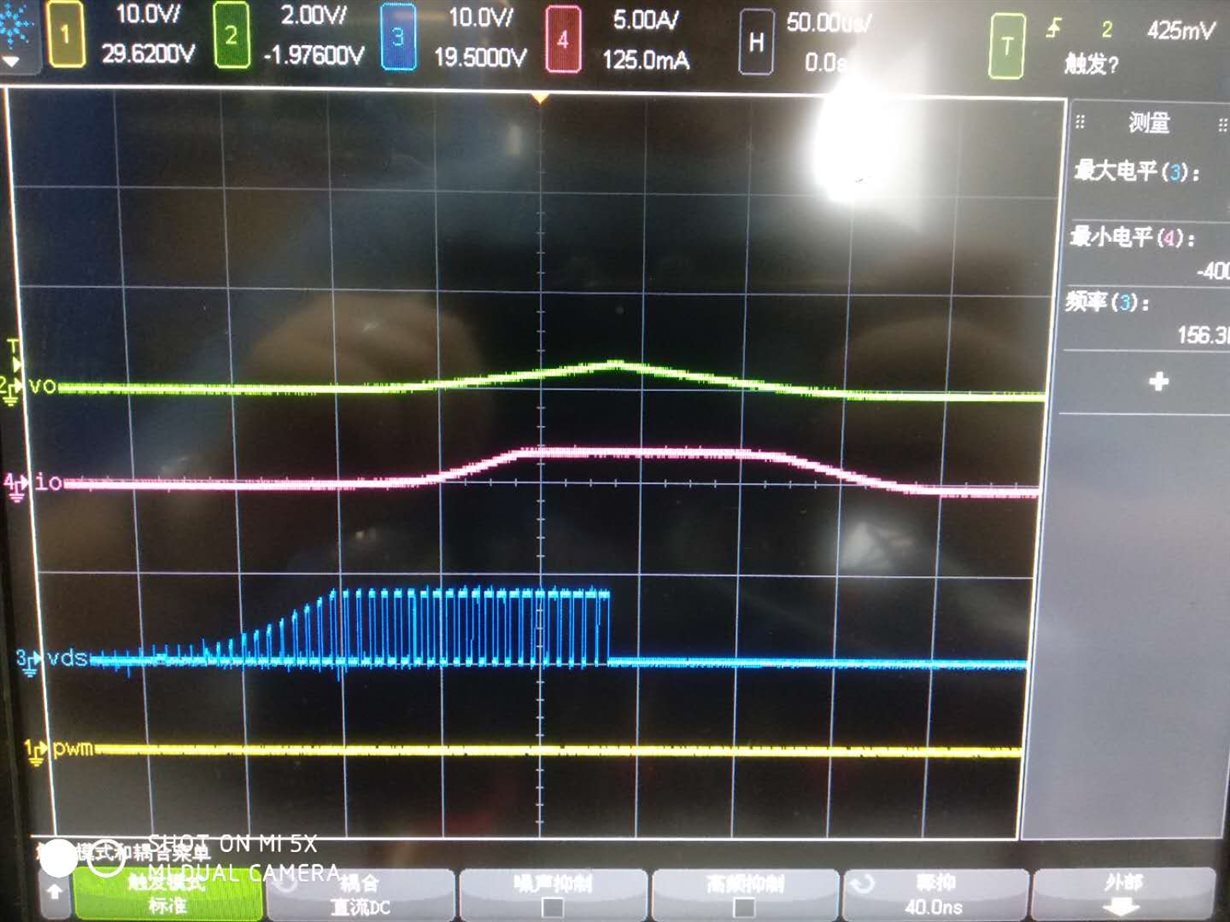

The second abnormal phenomenon is that at the moment of turn-off, the DS pole of the secondary rectifier MOS tube will have a large spike, and the output current Iout will flow in the reverse direction, as shown below:

As shown in the figure above, when Vout turns off to 0V, the DS pole of the secondary rectifier will produce a spike of nearly 100V. I do n’t know how to eliminate this spike?

As shown above, at the moment of turn-off, Iout will have a reverse current of 3A, how to eliminate this reverse current?

Please also advise, thank you.