Hi all,

I'm trying to evaluate the LMG5200 on an in-house PCB (single layer) and VIN, PGND, and SW short when I apply 28VDC at VIN. I've verified AGND and PGND are electrically isolated on the PCB and have been using a 677R load to PGND. The circuit seems to work perfectly up to VIN=25VDC but fails at VIN=28VDC. Does anyone know what I'm doing wrong here?

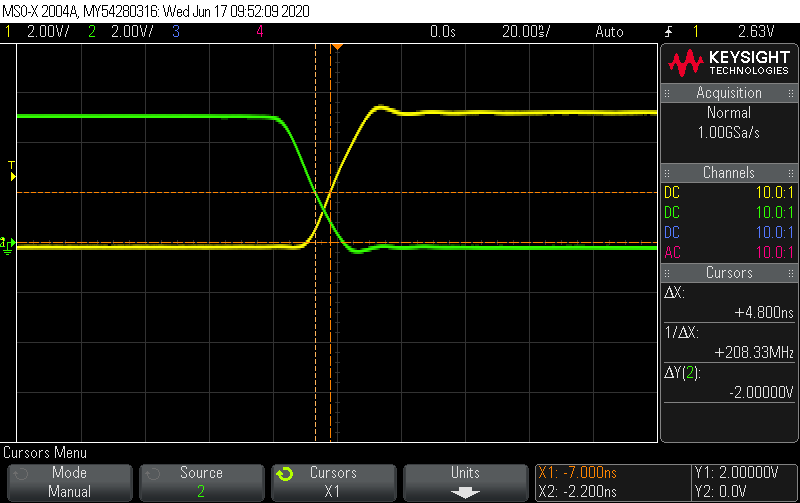

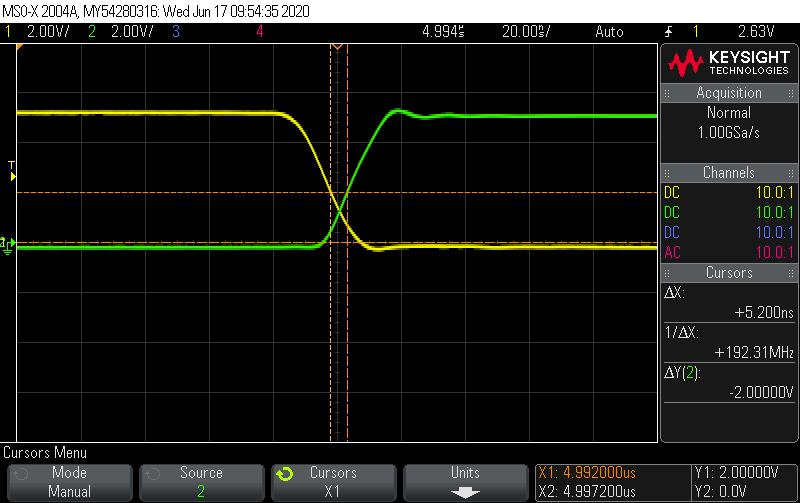

LI and HI are 100kHz, 5Vp, 30%DC pulses, offset to create 2uS deadtime.

VCC is 5VDC with 20uF to AGND.

Bootstrap cap is 0.1uF.

VIN has been tested at 12VDC, 22VDC, 25VDC, and 28VDC with 20uF to PGND.

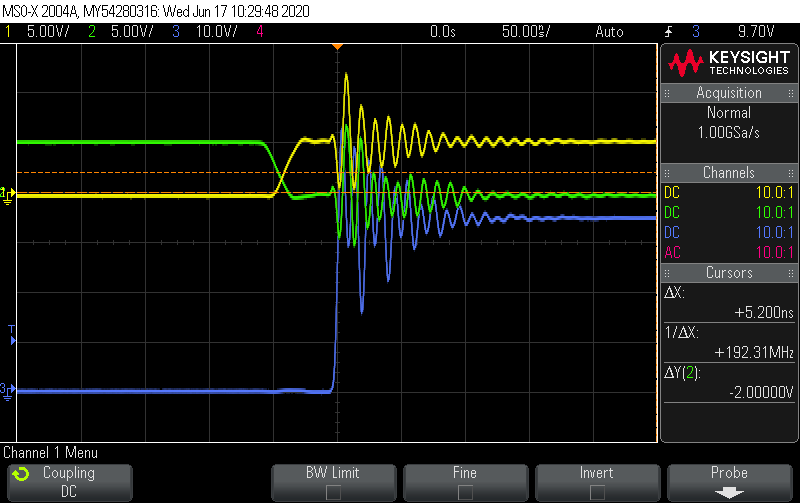

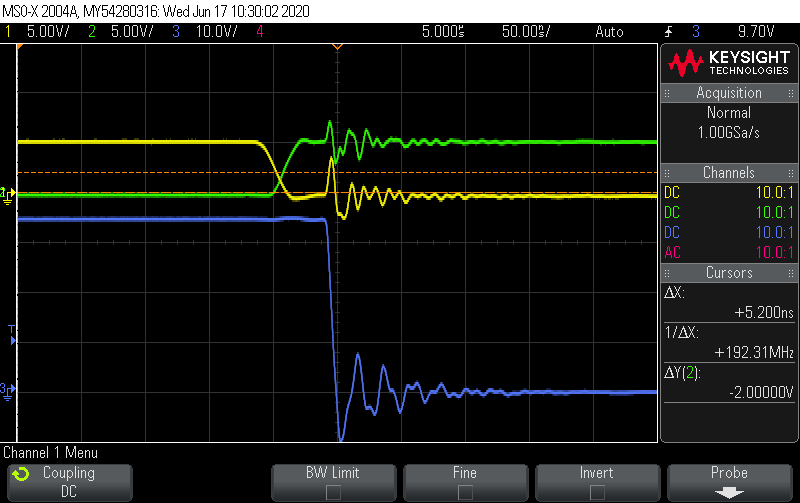

I have noticed not insignificant ringing on the inputs and outputs. A different forum thread I read suggested this was related to AGND and PGND being connected on the PCB, but this is not the case here.

Below is a scope capture of HI and LI v. SW (@25VDC VIN).