Hi,

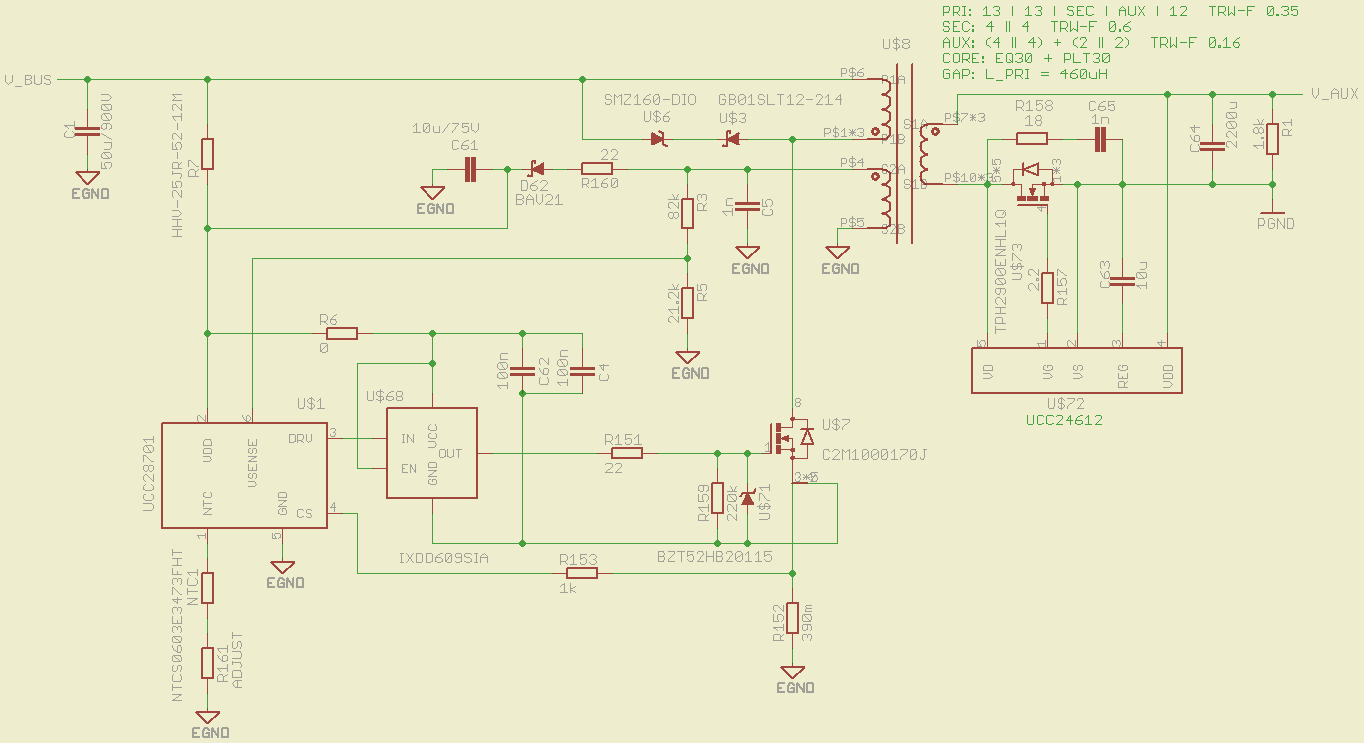

I am prototyping a 14V/4A flyback based on the UCC28701. It works mostly correctly, but I can observe the following mysterious behaviour:

1. At no load with 320V at the input, the converter enters the sequence of many cycles of restarts. It is ultimately terminated and 15.5V is present at output. If I decrease the dummy load resistor at the output to a value ~2 times smaller than calculated from the equations given in the datasheet, it starts in a reliable way.

2. If I_out is smaller than about 3A, the output voltage is close to the desired value and rock-stable across the entire range.

3. If the load resistance is decreased to make I_out exceed the 3A limit, the controller enters the restart sequence again.

4. If the load is further decreased, the controller enters a stable region again and outputs ~9.5V at a constant current of 4.1A.

As described above, the transition between CV and CC is not smooth and the transition region where the controller refuses to operate is pretty wide. What might be the cause of this behaviour?

If you can also explain the hiccup mode in (1), it would be highly appreciated as well.

If more details are needed, just ask. Here are some:

L_pri=405uH, N_pri/N_sec=9.5 (38pri:4sec:6aux),

R_cs=350mOhm

R_lc=1k

R_s1 (top) =82k

R_s2 (bottom) =20k

V_in = 180..900V DC

V_in_run=117V DC

V_dd = ~20V

Best regards, Piotr