We have a board that closely replicates the LM5060EVAL design.

We have the OVP slightly higher, at 62V. When we raise the voltage up to this threshold the LM5060 properly trips and shuts off the FET. But then it proceeds to let its smoke out... Visible destruction of pin 2 (VIN).

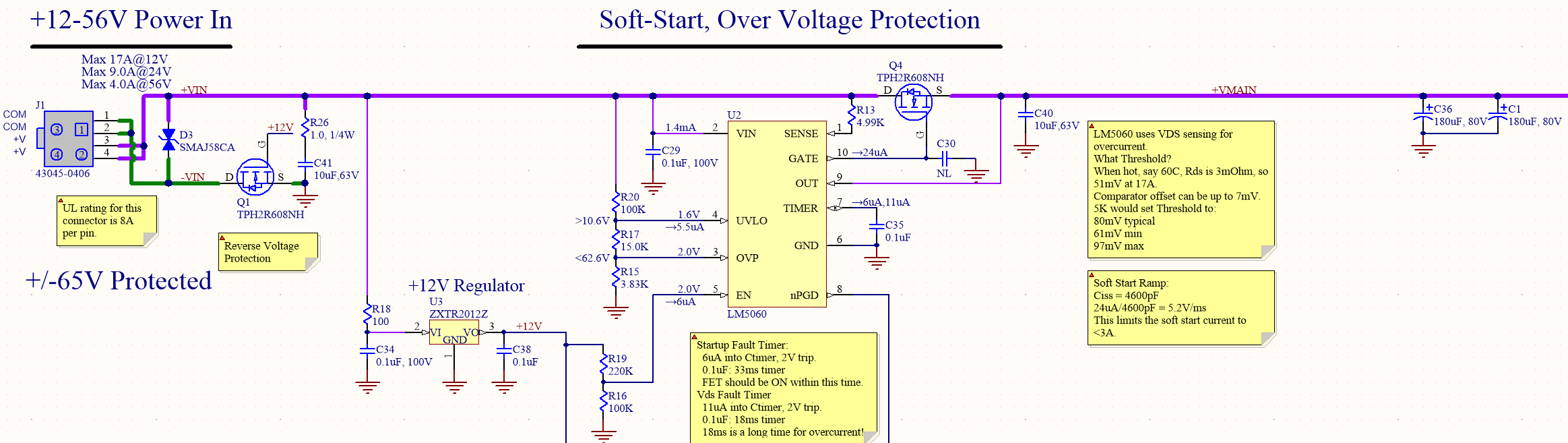

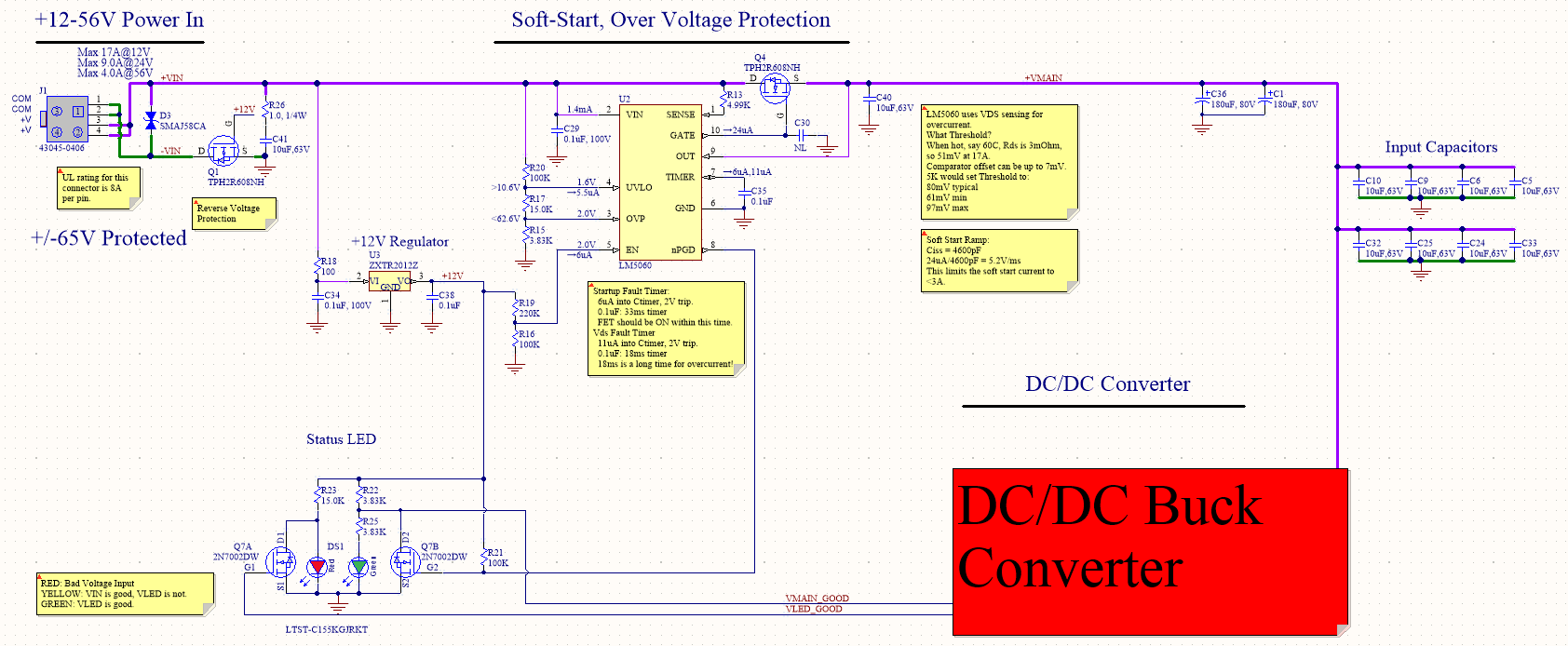

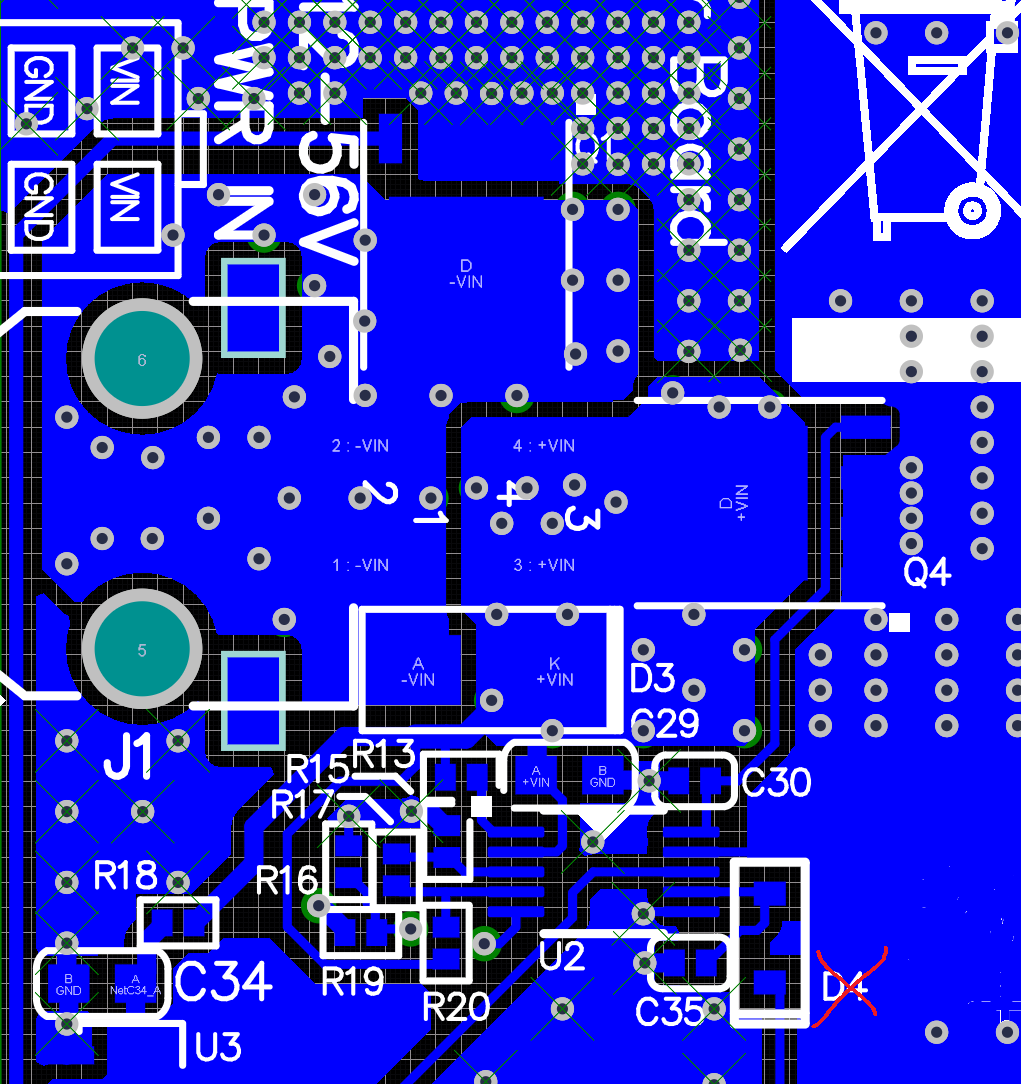

We have tried many many things, but are at a loss as to what is going on here. This is a snip of our schematic:

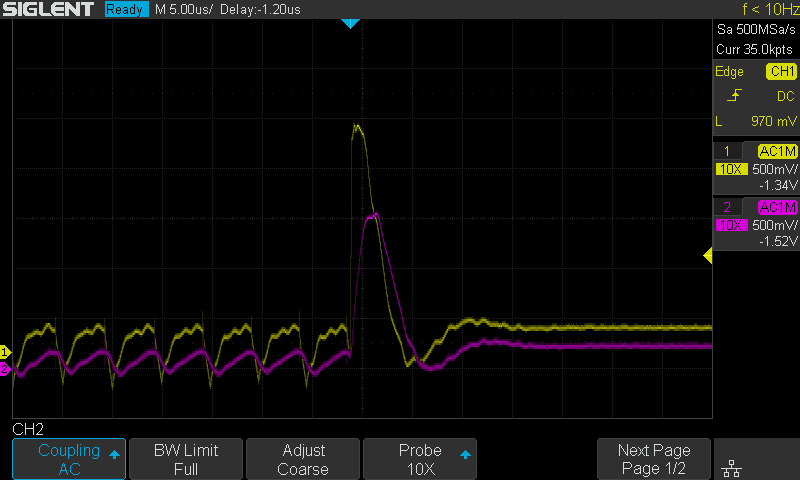

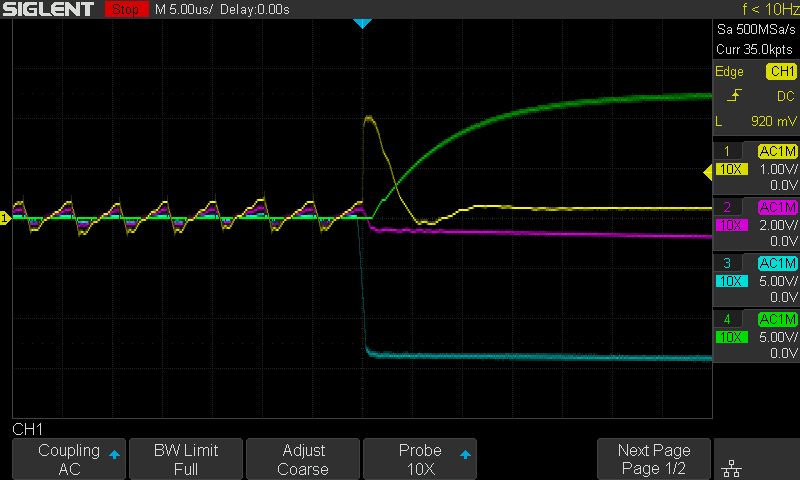

We have done through dozens of LM5060's trying to get this figured out. The issue appears to be worse with a load, though this is not required. We have scope captures of the +VIN and +VMAIN when the OV trip occurs and the inductive kick is only a couple volts. Another possible clue is that the nPGD signal (with 100K pullup to 12V) goes to the gate of a 2N7002 FET, and this FET is often damaged after the failure. Perhaps a higher voltage escapes nPGD when the LM5060 fails?

But the weirdest observation is also the most repeatable: A brand new board blows on the first try when +VIN is raised to 63V. Then we replace the LM5060, and the board is forever good. The new LM5060 always works properly and never fails again. We can't come up with an explanation for this observation, but it has been repeated many times. Does this make any sense?

Thanks!