Dear Team of PMIC support,

I'm not sure why a state transition ACTIVE -> SAFE instead of a transition ACTIVE -> RESET should occur, if (WD_FAIL_CNT=7+1 & WD_RST_EN=1) and (NRES_ERR=1).

Assuming the PMIC is in state ACTIVE and the watchdog tries to set NRES = 1 but NRES keeps 0 instead due to any random fault.

According to figure 6 in the TPS65381's datasheet from my point of view in this case there are two possible state transitions:

(T1) ACTIVE -> SAFE as NRES_ERR=1, provided DIS_NRES_MON=0 // Priority III

(T2) ACTIVE -> RESET as (WD_FAIL_CNT=7+1 & WD_RST_EN=1) // Global Reset Condition , Priority II.

But as T2 is of higher priority than T1 in this case T1 would not happen.

So my question is, in which cases transition T1 is taken?

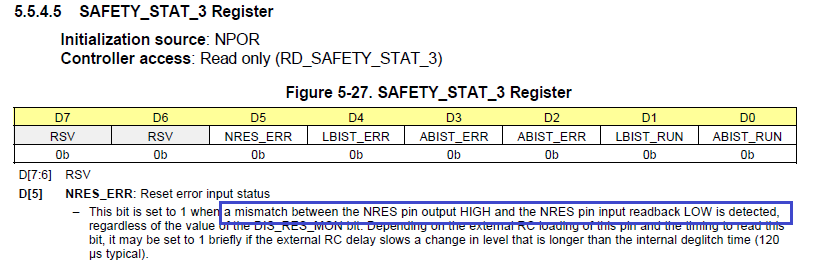

Maybe the answer is already given by figure 5-14 in which NRES_ERR is driven in two cases covered by the XOR gate and not just the case called in section 5.5.4.5.

Thank you in advance for your support

Stephan