Other Parts Discussed in Thread: UCC27712

Hi

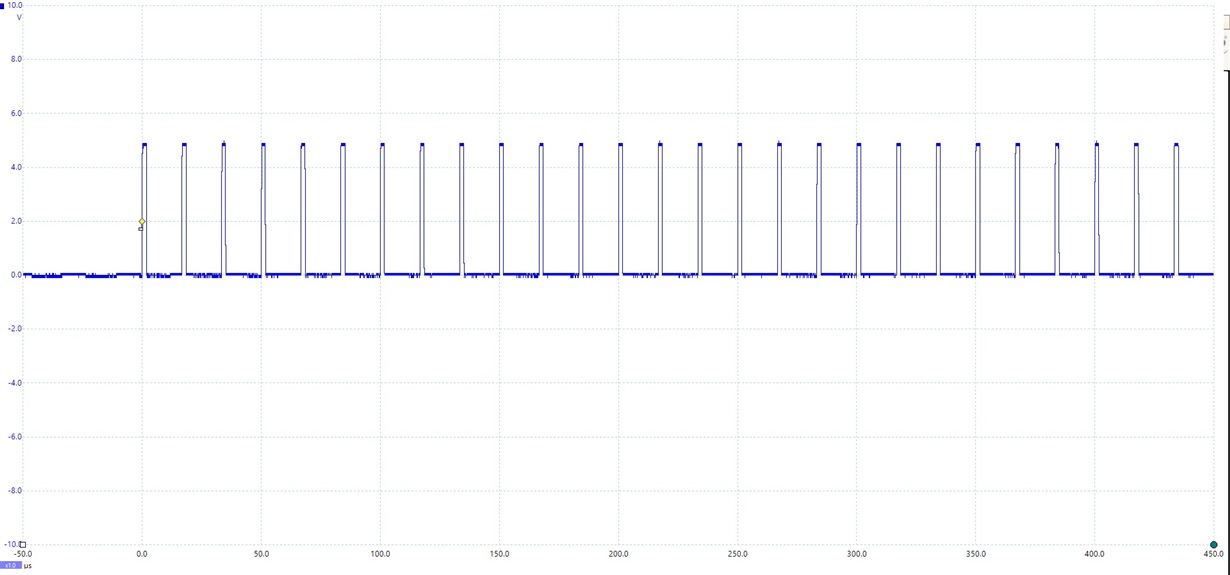

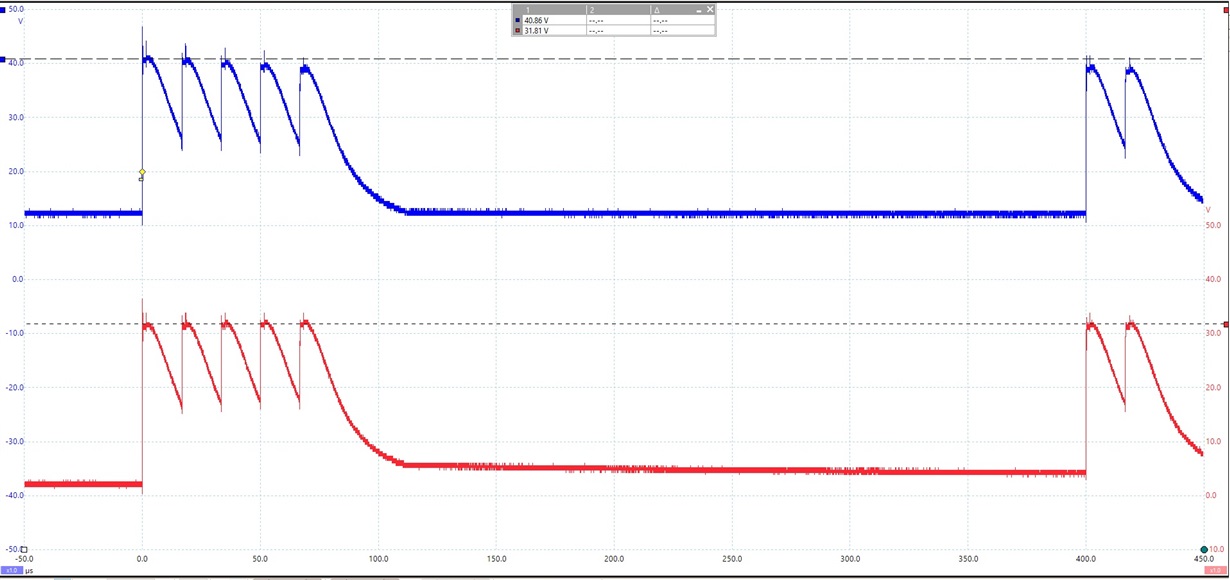

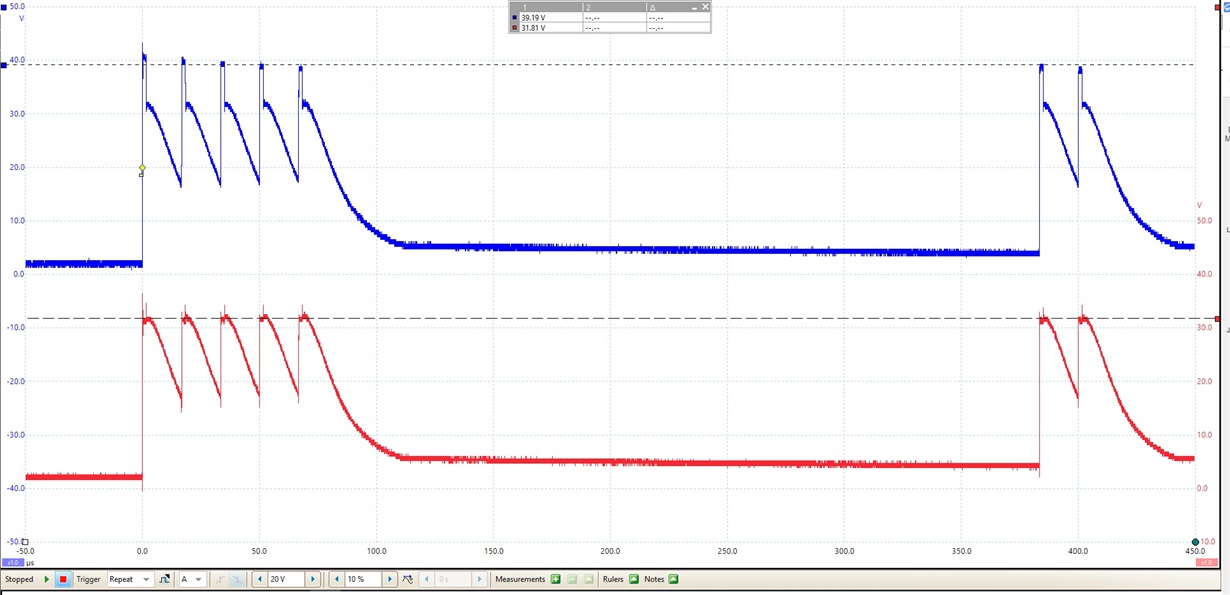

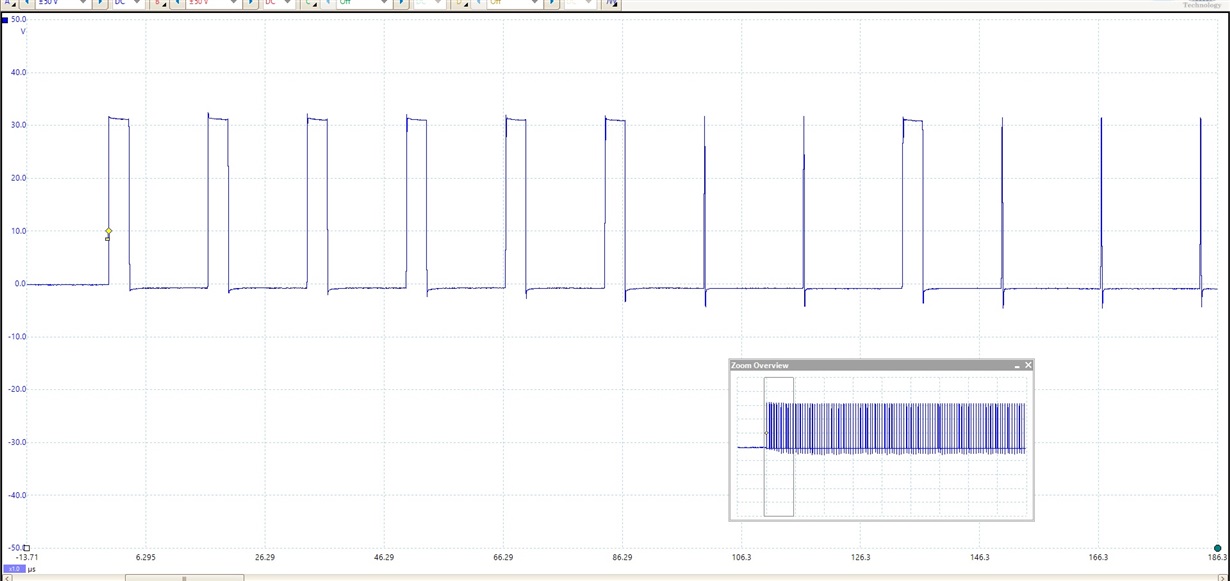

I have the low side fets switching fine, but the high side ones are not doing much, below is this portion of the schematics:

Mosfets are FDP61N20

U8 is the UCC27714

U9 is isolation ISO7730FDWR

D26 is standard diode VS-3EMU06-M3/5AT

Other diodes are shottky DSS120UTR

Please can you let me know if you find anything wrong?

Thanks