Hi,

The LM5060 device rapidly pulls the gate voltage low during startup as the GATE pin reaches the VGS threshold and the external mosfets Q1A and Q1B begin to conduct. This happens repeatedly until the output capacitor is charged to the input voltage. The first waveform below shows this behavior, and the following waveforms show evidence that EN, OVP, and TIMER never reach a condition where GATE should be pulling low.

CH1 (yellow) is the gate voltage - it charges to around 2.2 volts, then rapidly discharges.

CH2 (blue) is the output voltage. The output voltage eventually reaches the input voltage (10v). Side note: for higher voltages (~30v), the output never stabilizes.

CH1: voltage on the TIMER pin. The voltage never gets near the 2V threshold.

CH1: voltage on the OVP pin. The voltage remains well below the 1.6v threshold for OVP triggering.

CH1: voltage on the EN pin. EN remains above the 2v enable threshold.

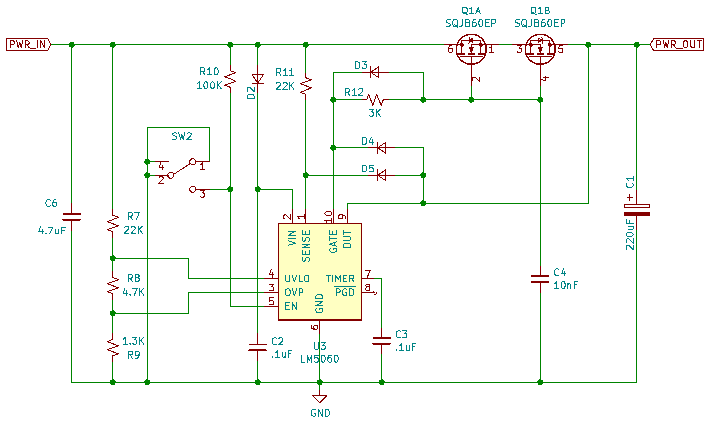

Since none of the documented reasons for GATE pulling low were occurring, I suspected the gate voltage was pulling low due to noise coupling into the LM5060 circuitry. I added capacitance at the most likely location of high frequency noise: the source pins of the mosfets (C5 below):

With this additional capacitance, the slew rate of the source pin and associated noise is reduced, and the GATE pin does not pull low. The output capacitor charges as expected:

CH1: voltage on the GATE pin

CH2: output voltage

Adding a capacitor across VDS of Q1A is not a safe solution: if a 30V power source is hot-plugged into the device, the source node will raise to 30V while gate remains at 0, and the VGS maximum will be exceeded. I experimented with capacitance from source to ground too - but that made the situation worse by coupling more noise into the LM5060. Maybe that would work with a clever ground path layout.

Is this noise coupling and GATE pin discharge a known issue with the LM5060? Any suggestions for other ways to reduce noise coupling or otherwise eliminate this startup GATE discharge?

Thanks!