Other Parts Discussed in Thread: TDA4VM

Dear TI Team,

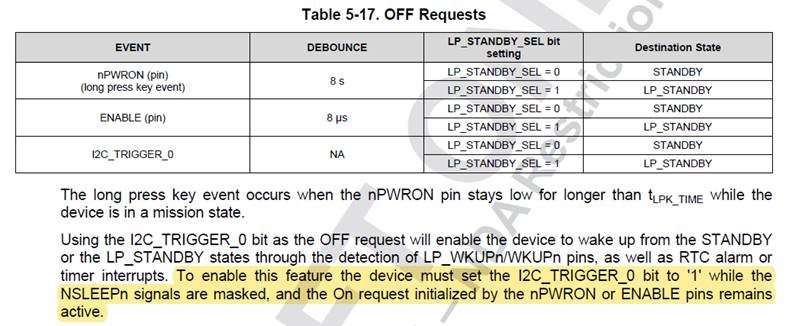

I want to send the OFF Request with I2C to the PMIC (From TDA4VM A72 Core) and I found the following infromation in the datasheet:

With this I concluded the i2c command that I Need to send can be the following, Could you please tell me If I am correct here or I need to consider something else?

#Unlock the register /usr/sbin/i2cset -f -y 2 0x48 0xA1 0x9B #Send the Off request /usr/sbin/i2cset -f -y 2 0x48 0x85 0x01

Thanks,

Pouyan