Hello Engineers,

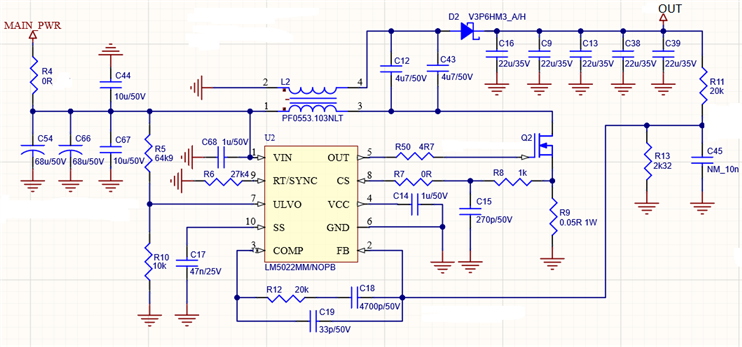

I have built sepic converter based on www.ti.com/.../PMP7305

Unfortunately Q2 burned up few seconds after power up. Before that I was able to measure output voltage - it was something about 60V without any load.

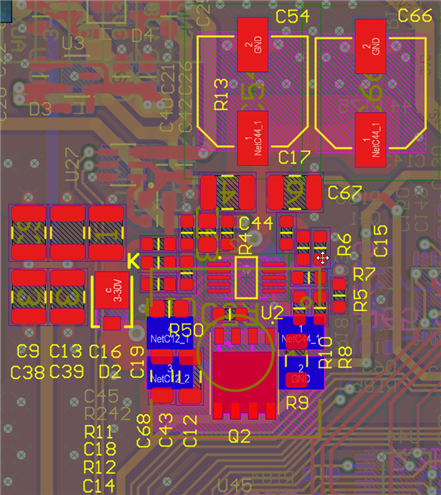

This is how my design looks like:

| Designator | Name | Footprint | Part number |

| C54, C66 | 68u/50V | HA0 | HHXC500ARA680MHA0G |

| C9, C13, C16, C38, C39 | 22u/35V | C1210 | GMK325BJ226MM-P |

| C14, C68 | 1u/50V | C0805 | UMK212B7105KG-T |

| C12, C43 | 4u7/50V | C1206 | UMK316AB7475KL-T |

| C15 | 270p/50V | C0603 | CC0603KRX7R9BB271 |

| C17 | 47n/25V | C0603 | CC0603KRX7R8BB473 |

| C18 | 4700p/50V | C0603 | C0603C472K5RACTU |

| C19 | 33p/50V | C0603 | C0603C330K5RACTU |

| C44, C67 | 10u/50V | C1210 | UMK325AB7106KM-T |

| D2 | V3P6HM3_A/H | SMP_DO220AA | V3P6HM3_A/H |

| L2 | PF0553.103NLT | PF0553.103NLT | PF0553.103NLT |

| Q2 | BSC065N06LS5ATMA1 | TDSON-8 | BSC065N06LS5ATMA1 |

| R5 | 64k9 | R0603 | CR0603-FX-6492ELF |

| R6 | 27k4 | R0603 | CR0603-FX-2742ELF |

| R7 | 0R | R0603 | CR0603-J/-000ELF |

| R8 | 1k | R0603 | CR0603-FX-1001ELF |

| R9 | 0.05R 1W | R1206 | WSLP1206R0500FEA |

| R10 | 10k | R0603 | CR0603-FX-1002ELF |

| R11, R12 | 20k | R0603 | CR0603-FX-2002ELF |

| R13 | 2k32 | R0603 | RC0603FR-072K32L |

| R50 | 4R7 | R0603 | RK73H1JTTD4R70F |

| U2 | LM5022 | VSSOP-10 | LM5022QDGSRQ1 |

I'm going to replace Q2 but before that I have few questions:

1. Do you see any errors in above schematic and/or PCB?

2. Are there any steps that should I do when I will run it again to prevent burning up again?