Other Parts Discussed in Thread: ALLIGATOR, ,

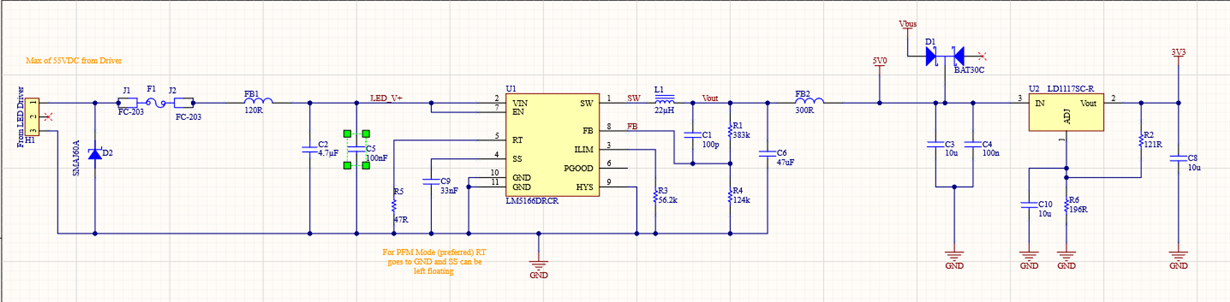

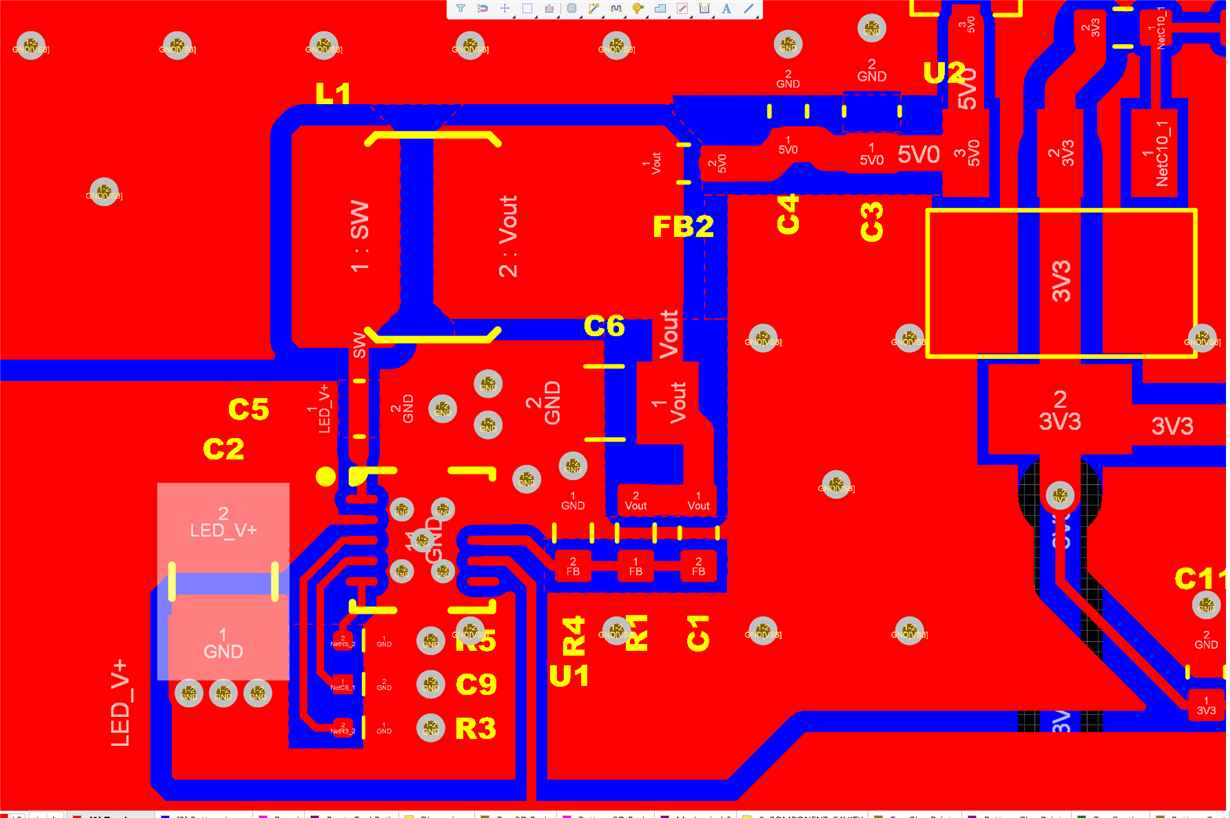

My original thread was closed (https://e2e.ti.com/support/power-management/f/196/t/914047) so this is a follow up to that thread where we discussed different layout options. I was able to come back to this project and do some initial power up measurements.

This is a scope trace across the output cap using a wire for ground (so very short ground wire and probe position). I am feeding the board with 15VDC with my bench power supply and it is consuming 43mA. I've offset the channel by 5.0V so I could zoom in on the noise.

I literally just brought the board up but I've been curious how the output signal would look like since I was told that running the switcher trace under the input cap would not cause any noise issues. I'm not saying that my noise is from that but I'm certainly surprised to see 100mV on my first measurement.