Hi Team,

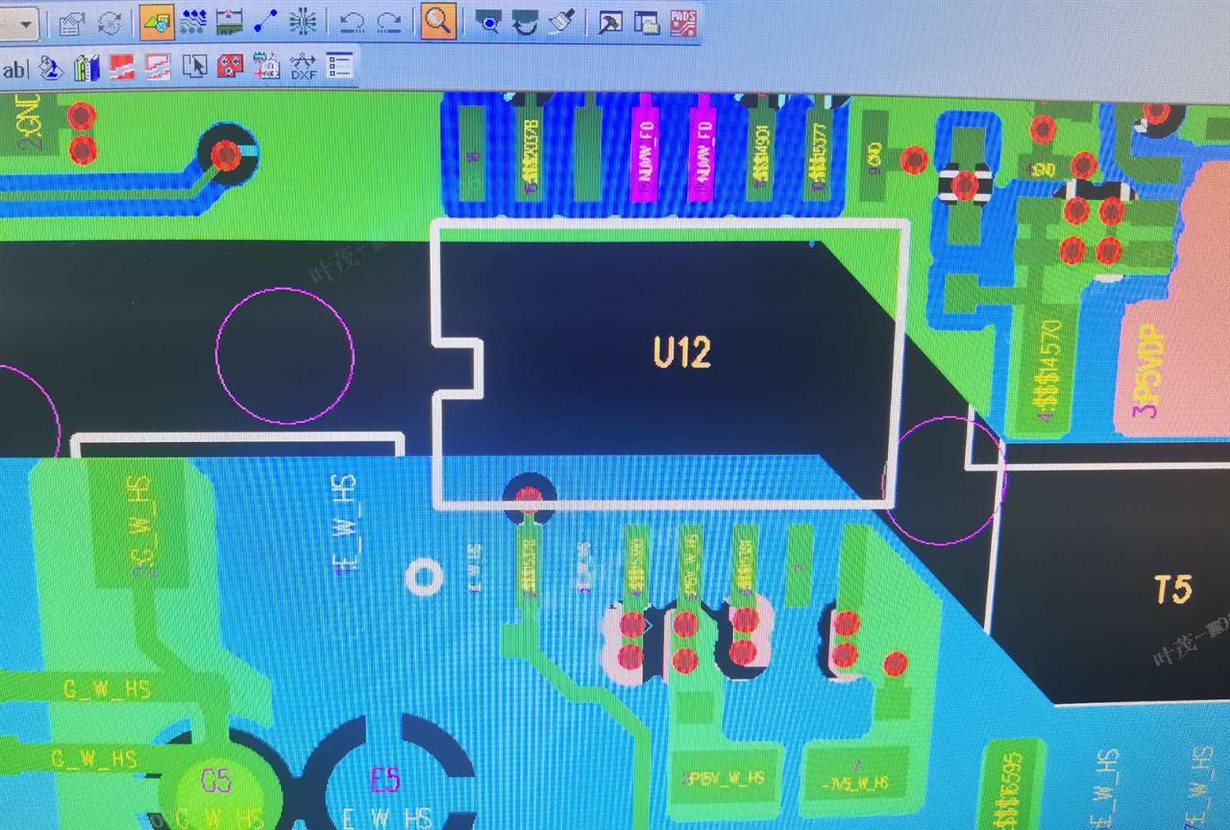

My customer now is evaluating UCC21750-Q1, and during the PCB layout, the copper is under the UCC21750-q1's body, PCB layout shown as below figure,

and in datasheet there is description that "No PCB trace or copper is allowed under the gate driver.A PCB cutout is recommended to avoid any noisecoupling between the input and output side which can contaminate the isolation barrier",

Could you kindly share more information how the PCB layout impact the isolation barrier?

Best Regards

Benjamin