Hi,

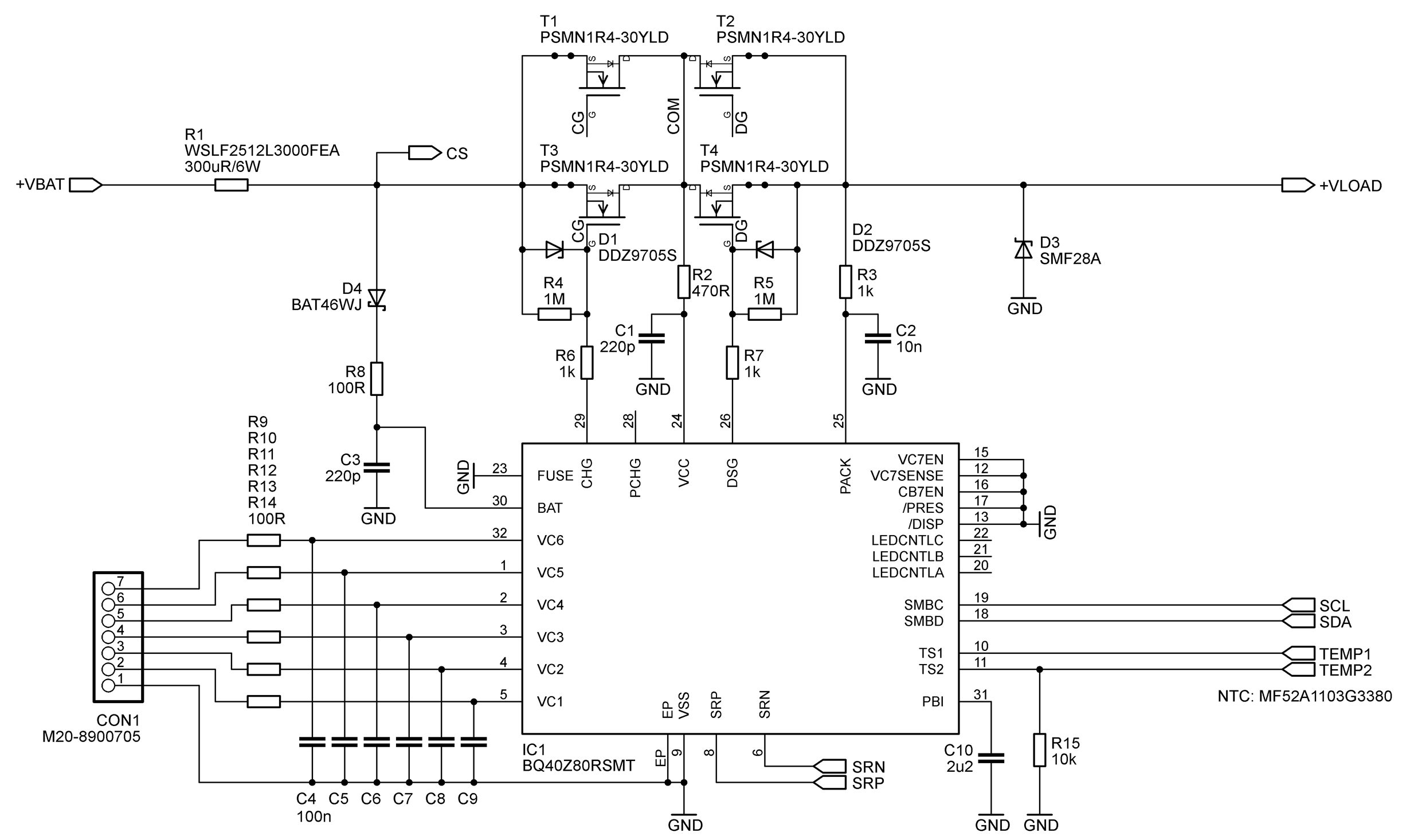

I kindly request a review of the attached design with respect to the correct BQ40Z80 wiring, and values of associated components. In particular, I am unsure about the values of these components:

- R8, C3, R6, R2, C1, R7, R3, C2.

I have a few other questions and remarks:

- the cell voltage sense connections including VSS (CON1) can make contact in any order, is this acceptable for the IC?

- the +VBAT power connection to the battery can be made before or after connecting CON1 during production, which order is preferable?

- the second temperature input (TS2) is active but not used, therefore a default 10k resistor (R15) is in place.

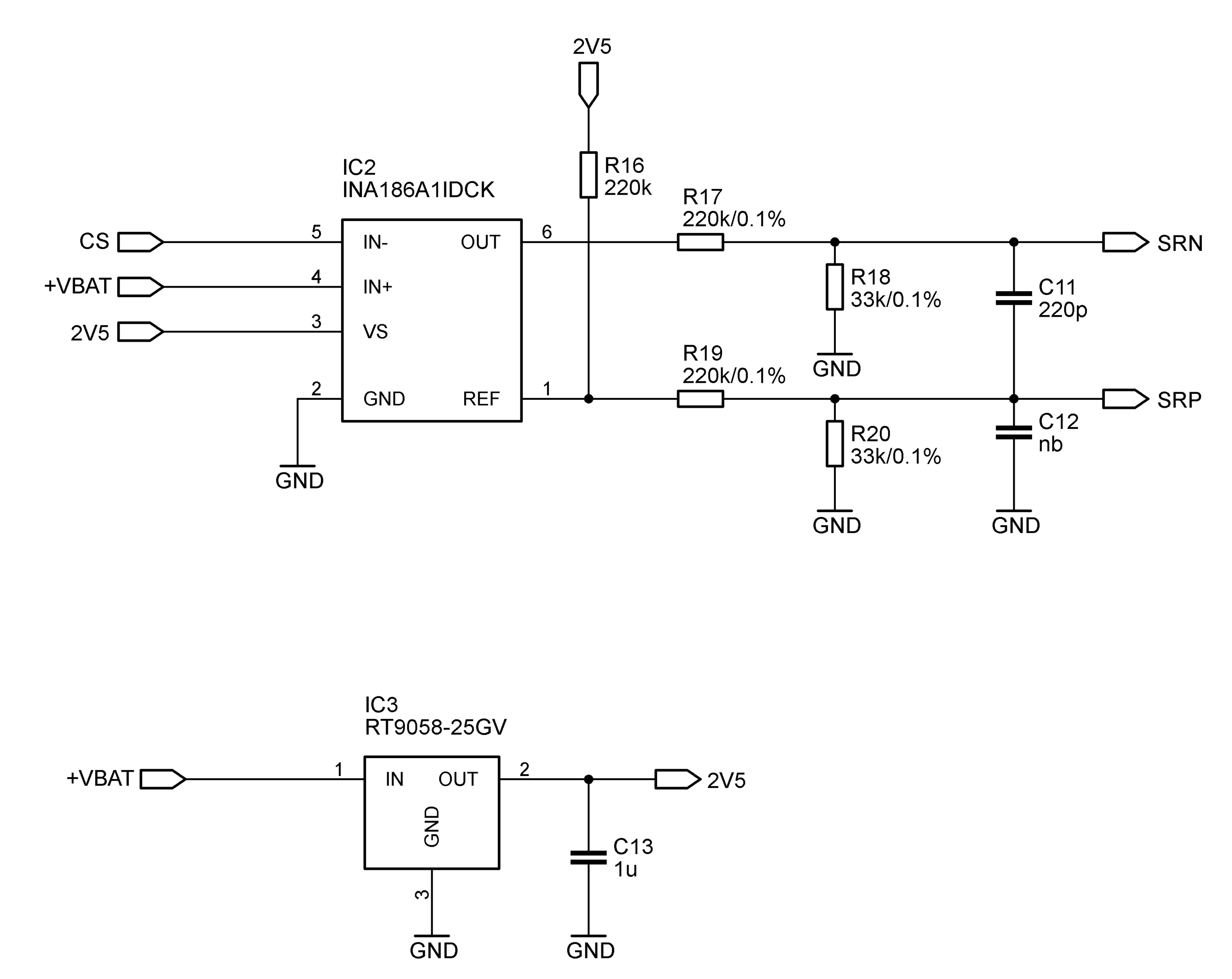

- the second page shows the high side current monitoring circuit for completeness, this part is fully evaluated and only provided for completeness.

Thank you in advance,

Regards

Frank Boeh

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.