Other Parts Discussed in Thread: UCC21750

Hi,

I have a question about active pull-down function of UCC21750.

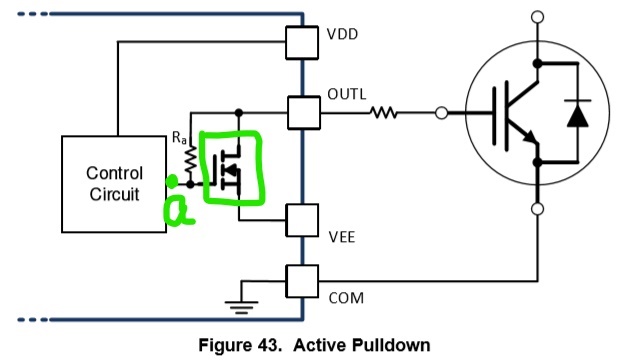

According to the datasheet, "ucc21750 implements an active pulldown feature to ensure the OUTH/OUTL pin clamping to VEE when the VDD is open. The OUTH/OUTL pin is in high-impedance status when VDD is open, the active pulldown feature can prevent the output be false turned on before the device is back to control."

Does the high impedance status mean pulldown capability? I am wondering whether high impedance status would effectively avoid false turning-on? What if the miller current (caused by the complementary switch's on/off transient) go through this high impedance?

Many thanks.

Bests,

Zack