Hi,

I would like to ask you about the selection of the input capacitor connected immediately after the bridge diode of the device of UCC28070.

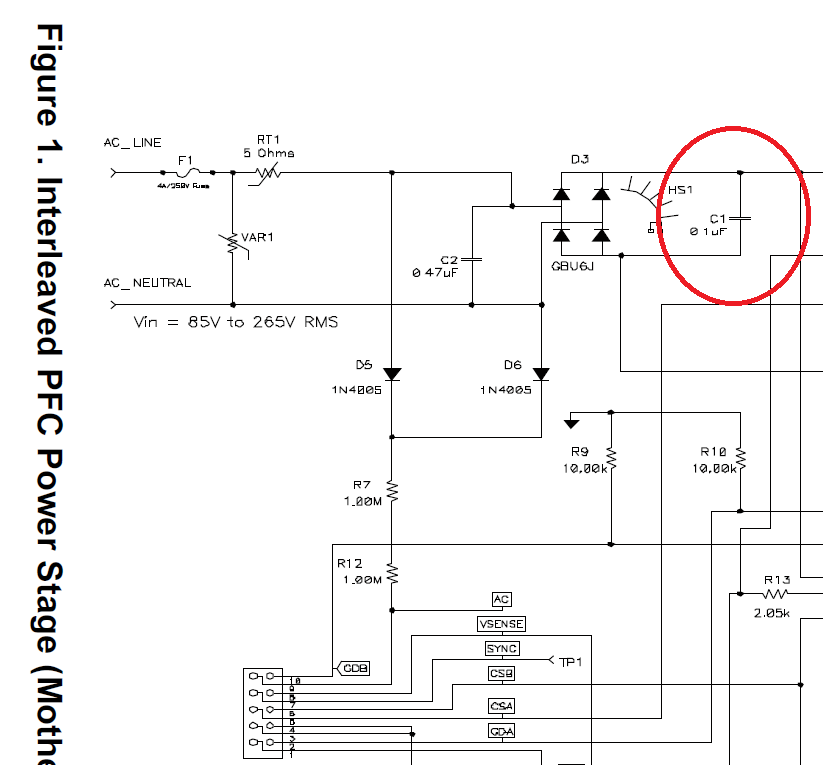

An excerpt of the EVM circuit is shown below, which corresponds to the 0.1uF (C1) indicated by the red circle.

In principle, since it is interleaved, it cancels each other out, so I think that it may be judged that the input capacitor may not be necessary, but in reality it is difficult to cancel 100%, so I think it is necessary to add some capacitance...

The circuit I made considers the worst condition and selects the input capacitor because the inductor ripple flows completely.

I use 1uF in parallel.

However, when measuring the current that actually flows, the elements that are canceled out are large, and the ripple current is sufficiently small, and it seems that the component margin has been taken too much.

Could you give me your opinion on how to choose the input capacitor?

Best regards,