Hi Jeffery,

I encountered a difficult problem these days and want to ask for your help.

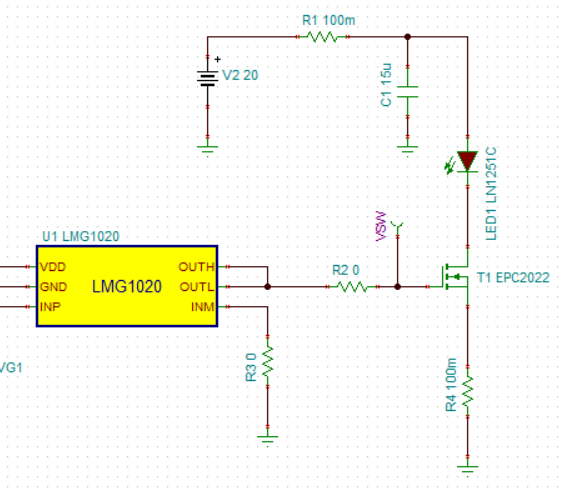

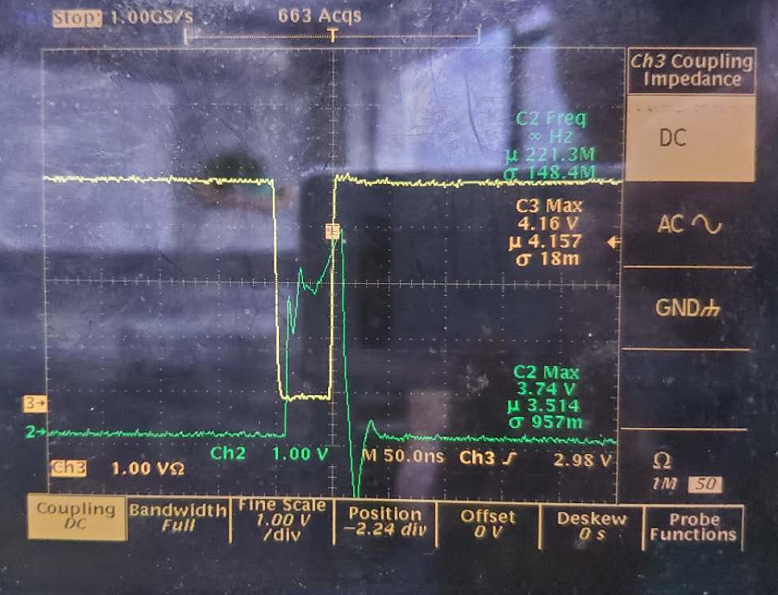

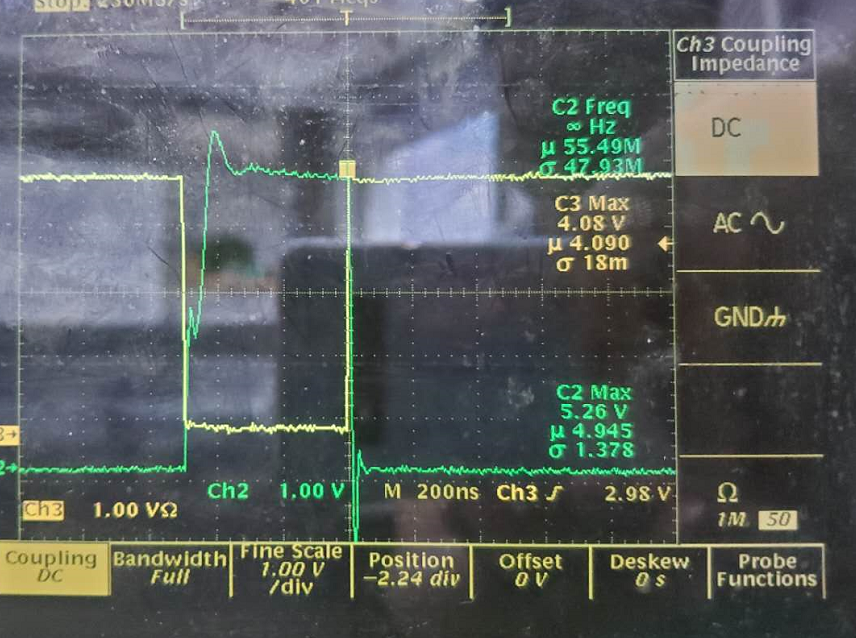

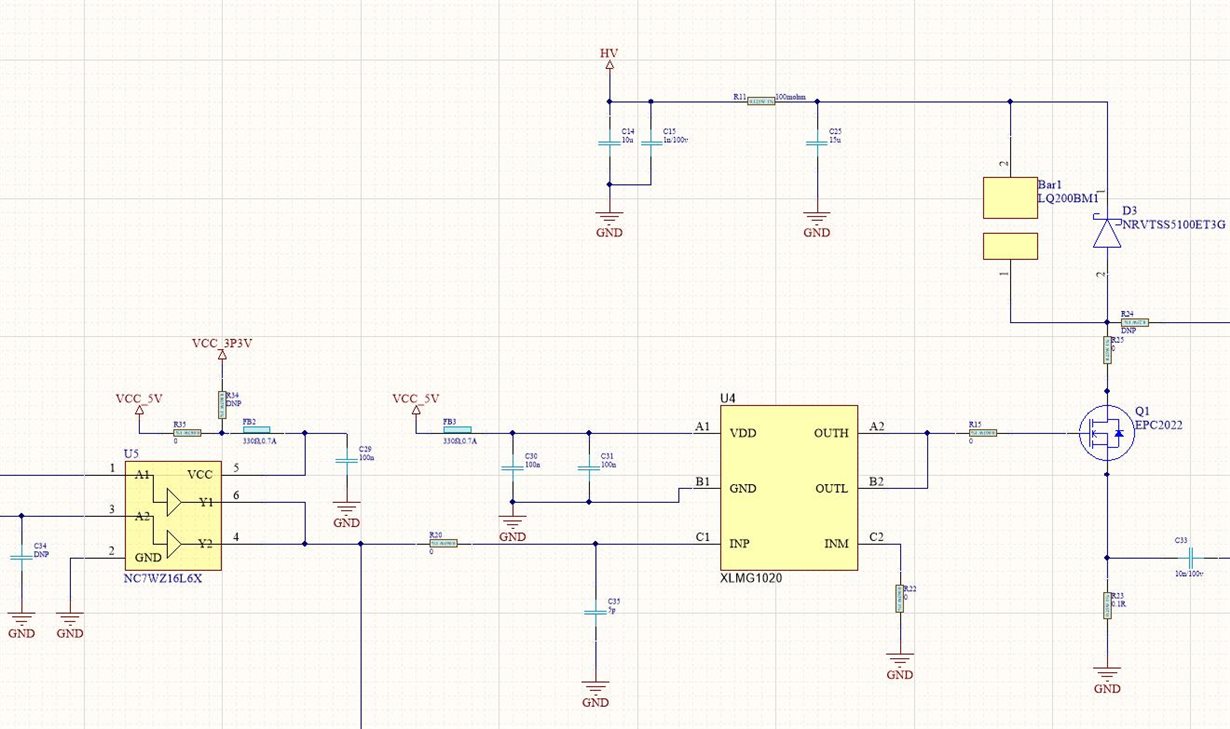

The problem is like this. As shown in the figure below, I use 1020 to drive epc2022 to control LD (here with LED instead). When R2 is disconnected and Vds is not powered, the driving signal is output at 4.8v after 1020, but when I connect R2 Other conditions are the same as above), the VSW signal amplitude is pulled down to 3v, I also replaced the MOSFET and the 1020 phenomenon is still the same, what do you think is the reason?