Other Parts Discussed in Thread: AM4378, TPS65218

I have a customer are using the TPS65218D0RSLT PMIC to support the AM4378BZDN80 Sitara.

They are seeing an issue we do not understand and are requesting your input and guidance per below description.

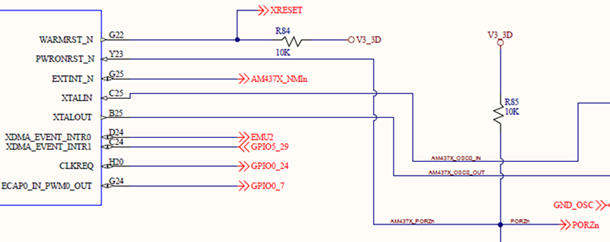

The PMIC receives a reset (pulled to ground by a switch…same as implemented in the AM437X GP EVM) through the WARMRST_N (called XRESET in our schematic below);

However, the PMIC DCDC outputs (other than DCDC5 and DCDC6) shut off and do not recover after the reset action until input power is cycled OFF/ON.

Do you have any thoughts/suggestions for us to continue our investigations?