Other Parts Discussed in Thread: CSD19537Q3

We are seeing some strange behavior with our TPS40170. Without going into all the detail about what we’ve seen and tried at first, I’m going to try and hit the main relevant (at least what we think are relevant) points:

Overview:

- We are using the TPS40170 as an adjustable buck regulator by adjusting Vtrk

- We are using 48Vin as our input, and want to vary the output between ~5V and ~40V out. Max current is <1A

- The output is adjusted relatively slowly – our RC filter on the Vtrk input has a time constant of ~10ms, and our SW limits the Vtrk change to a max of ~23mV every 50ms.

Issue:

- Sometimes, our low-side FET is being damaged: gate, drain, and source are all shorted together.

- We don’t understand what is causing this – we have been unable to measure any overvoltage condition on the switch node or the gate of the FET so far.

Ideas:

- Aside from slight ringing, we have yet to measure any kind of overvoltage on the FETs gate pin (high or low side) nor the SW node.

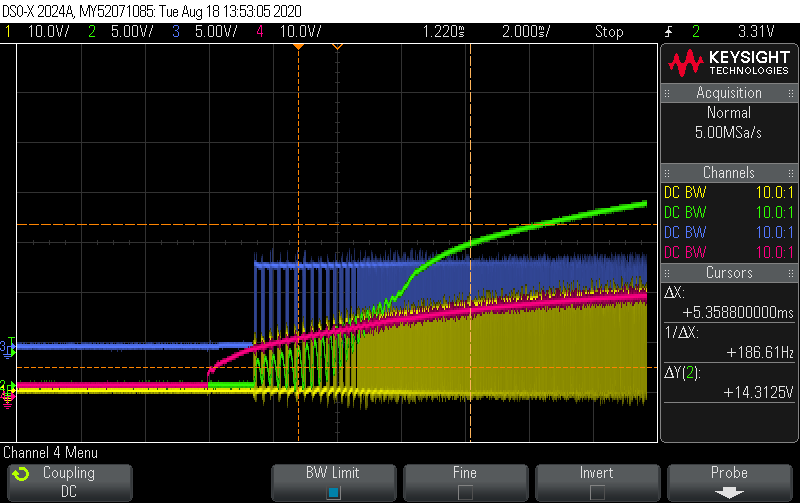

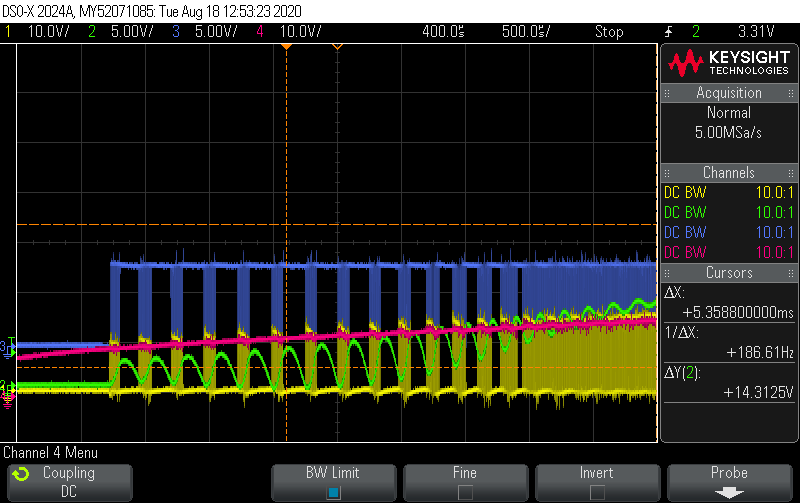

- We think we have caught some odd behavior of the TPS40170 upon startup (see scope shots below - the second is just zoomed in on the oscillations of the first).

-

- Yellow = SW node, Blue = low-side FET gate pin, Green = output voltage, Red = input voltage

- It looks like the supply tries many times (much more than 7, so I don’t think it’s overcurrent) to start regulating. But during each attempt, it turns the low-side FET on for ~200us after the output rises to ~5V, which takes the output voltage almost to 0. Every successive “attempt” makes the output voltage rise to a slightly higher maximum, until it looks like something finally kicks in and it behaves normally and regulates normally.

- If this were to happen with more than just 5V on Vout, it would surely damage the low-side FET. With just this 5V output, we are looking at ~40A pulled into the FET during that 200us. At higher voltages, I can easily see this issue causing the FET to dissipate on the order of 100mJ for each “attempt”.

- I can’t find anything in the datasheet that would explain this startup behavior.

-

- We also would like to understand what the datasheet means by: “For proper tracking using the TRK pin, the tracking voltage should be allowed to rise only after SSEAMP has exceeded VREF, so that there is no possibility of the TRK pin voltage being higher than the SSEAMP voltage”. Since we are using the TRK pin to adjust our output voltage, what should we do with it during startup / error conditions?

Thanks in advance for the help!

-Bill