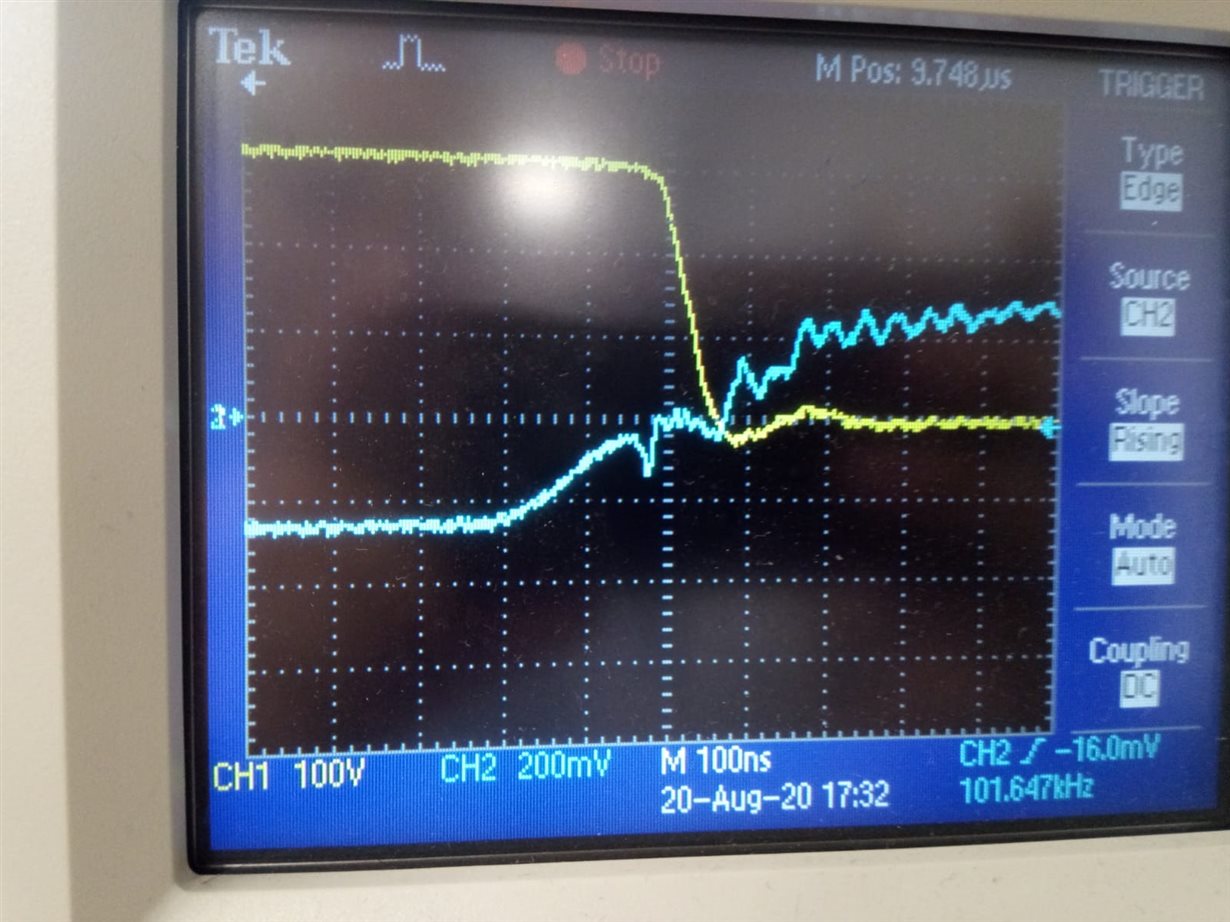

Hello Team , There are 3 different cases in the picture as you see below.

Yellow Channel D-S

Blue Channel G-S

My question is why the miller effet so obvious is?

and does the ZVS achieve i could not understand cause of the miller effect.

1. Picture %35 Load , 2.Picture % 70 Load , 3.Picture %95 Load

Thanks in advance

Mikail Ünal