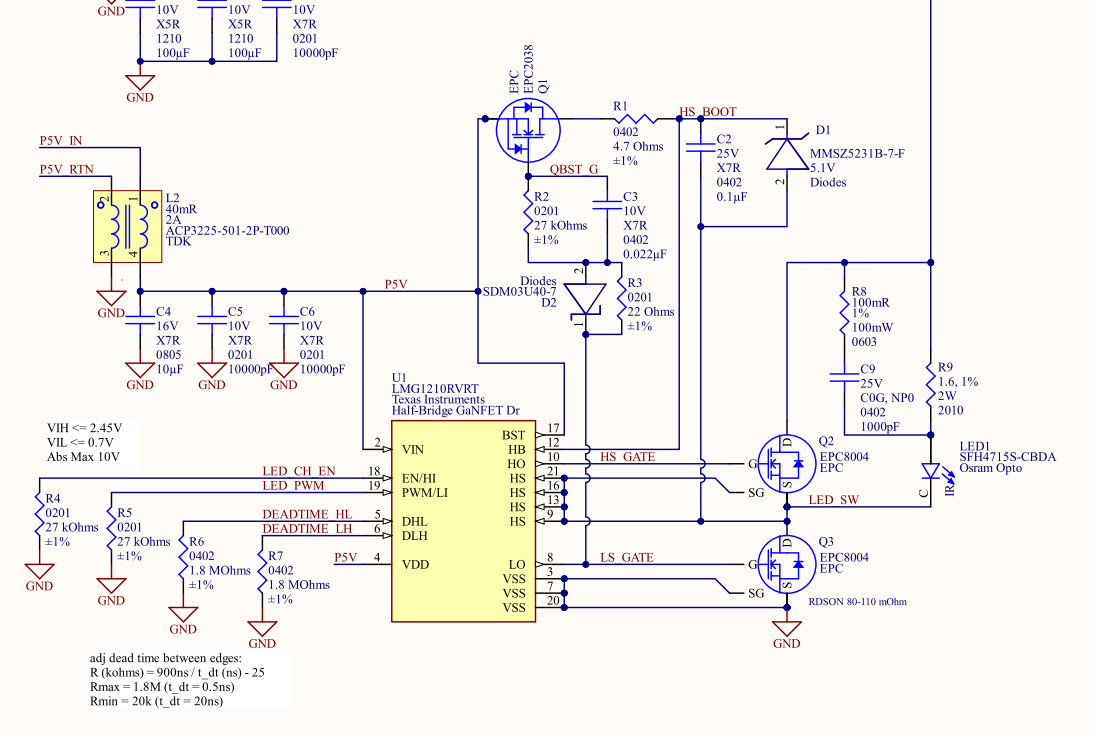

I have just received a board I designed that uses the LMG1210 with the synchronous bootstrap circuit shown in https://epc-co.com/epc/Portals/0/epc/documents/schematics/EPC9066_Schematic.pdf. This is the same circuit that is referenced in the answer to this support question.

I want my rise and fall time to be less than 5ns. Rise time is OK. Fall time is about 14ns. After a little debugging, I think this synchronous bootstrap circuit may be slowing the fall time of my switching node. Is there any more documentation regarding the recommended synchronous bootstrap circuit?

Rachel