Other Parts Discussed in Thread: BQ76942, TINA-TI

Hi,

I have been trying to achieve low-side FET switching, as there is no reference in datasheet.

I have followed following references in videos section called "BQ76942 / BQ76952 battery monitors: FET configurations and cell balancing"

And following thread

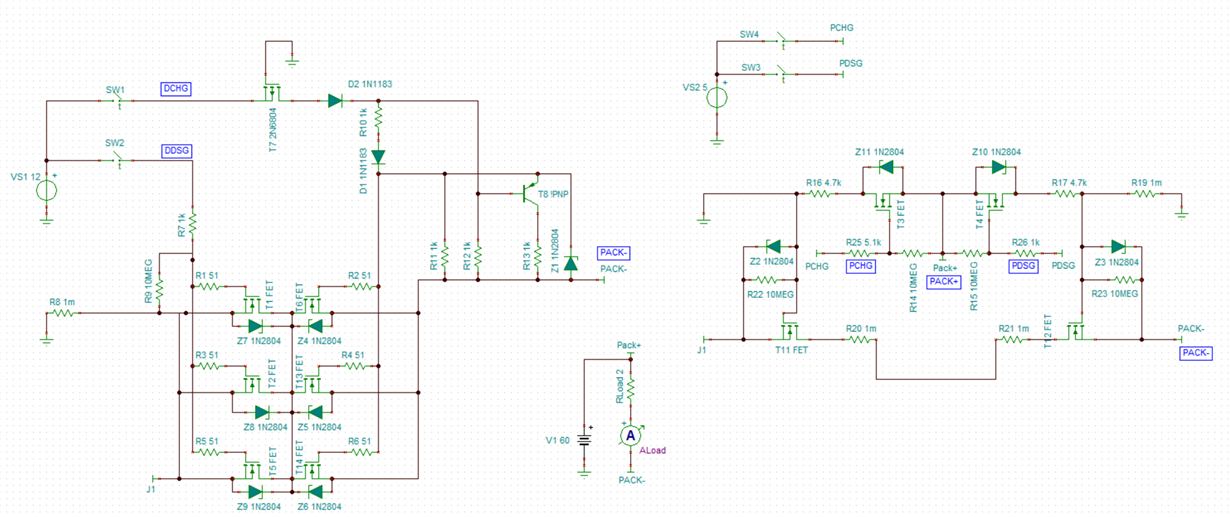

So far, I have created following schematic and need some help in verifying it:

I still need to calculate passive values.

Regards,

Anurag