Other Parts Discussed in Thread: LM5146-Q1

Hi

I'm using the LM5145 with two CSD19532 for my DCDC stage. I have two issues.

First

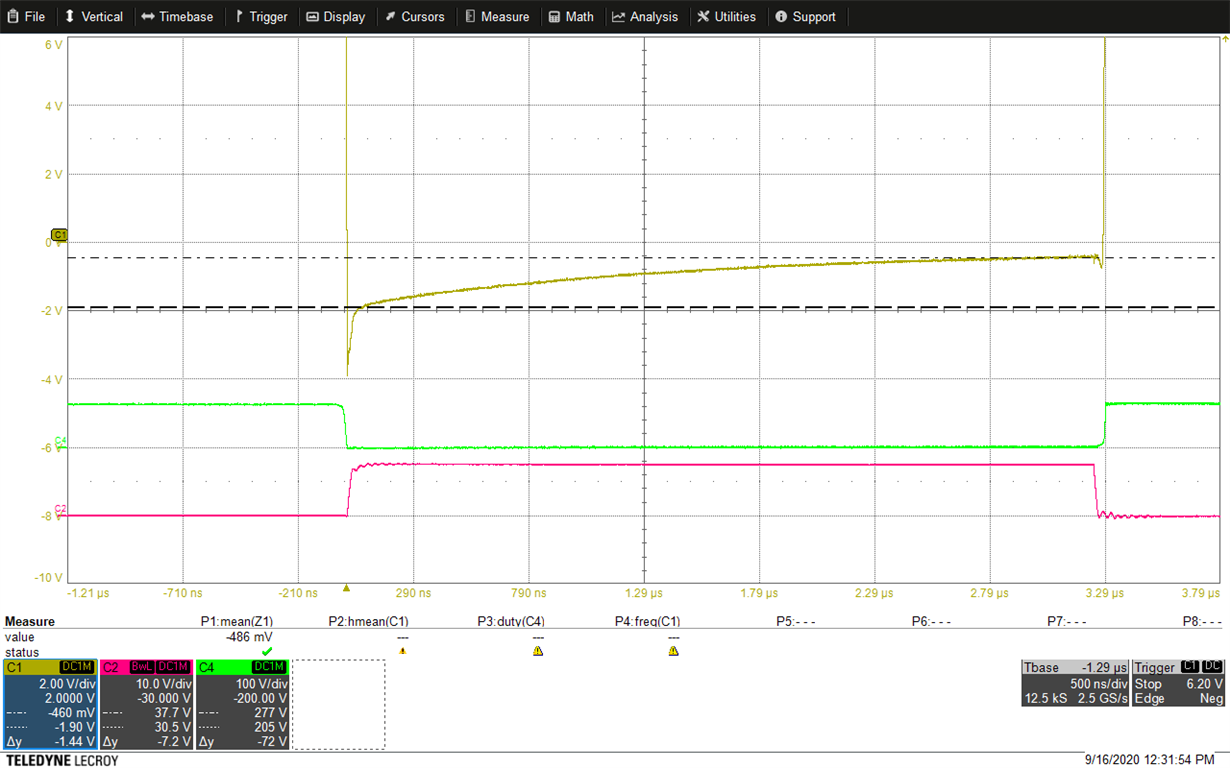

I have an over-/undershoot that I could reduce but it looks like that the solution (increasing gate resistors up to 33Ohm) is not the best way to solve it. Do you have an advice?

Second

When the low side FET is on, the negative voltage over the low side FET is larger as expected. Can you explain that?

Please check the attached word file. I have added all information into this document.

BR

SilvanoDCDC_Stage_Issue.docx