Other Parts Discussed in Thread: UCC27524

Hi,

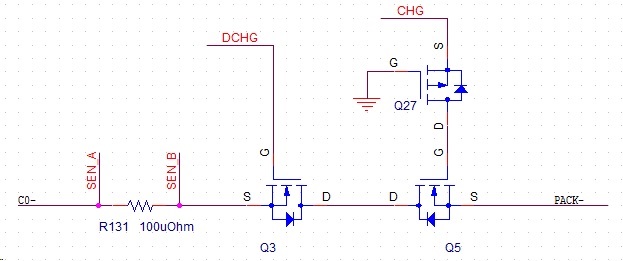

We are developing 30S BMS and control the charge and discharge flow on low side using MOSFET. We need support on selection of MOSFET and Driver for charge current of 80A and Discharge current 200A. The max bus voltage is 150V.

The FETs will be controlled directly by microcontroller using Driver.

1. Which driver will be suitable for this applicaiton,

2. How we can decide, when to turn ON/OFF FET?