Other Parts Discussed in Thread: LM5101, UCC27282, LM5106

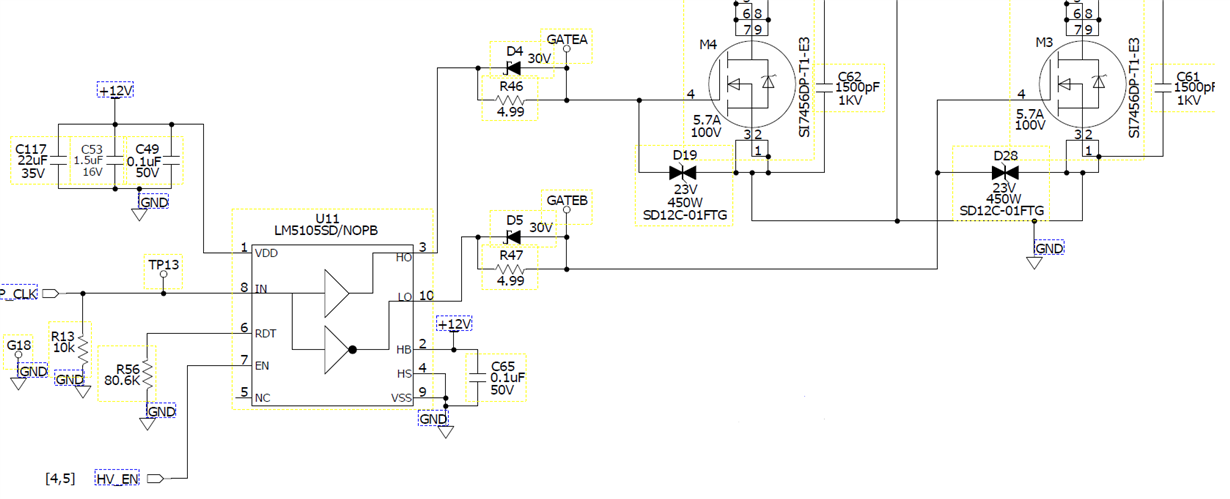

Basics:

Operating frequency is 125kHz

VDD and HB are +12V

Problem statement:

From 470ns to 520ns the falling edge of the clock tracks the falling edge of the HO pin with increasing propagation delay between them from 60ns to 68ns. This isn't an issue for us and the result is nearly identical on the LO pin. We aren't presently operating below 470ns.

Once you cross the 520ns threshold, the falling edge of the HO pin "snaps back" as seen in the video and you now have a constant propagation delay of 26ns for all increasing duty cycles.

This is an issue for us and causes severe instabilities in operation and loop tuning.

I have placed a video in here, but it doesn't look right. Please let me know if you can't see it and how to get you the video. I could create a dropbox link if that will work for you.

Additionally, I have limited the amount of data to you to help prevent info overload. Please let me know of any additional details you might need and I will gladly try to provide them.