Other Parts Discussed in Thread: BQ76952

Hi, my problem is with the cell balancing feature of bq76942.

I like to use the automatic balancing, but host controlled would be fine to.

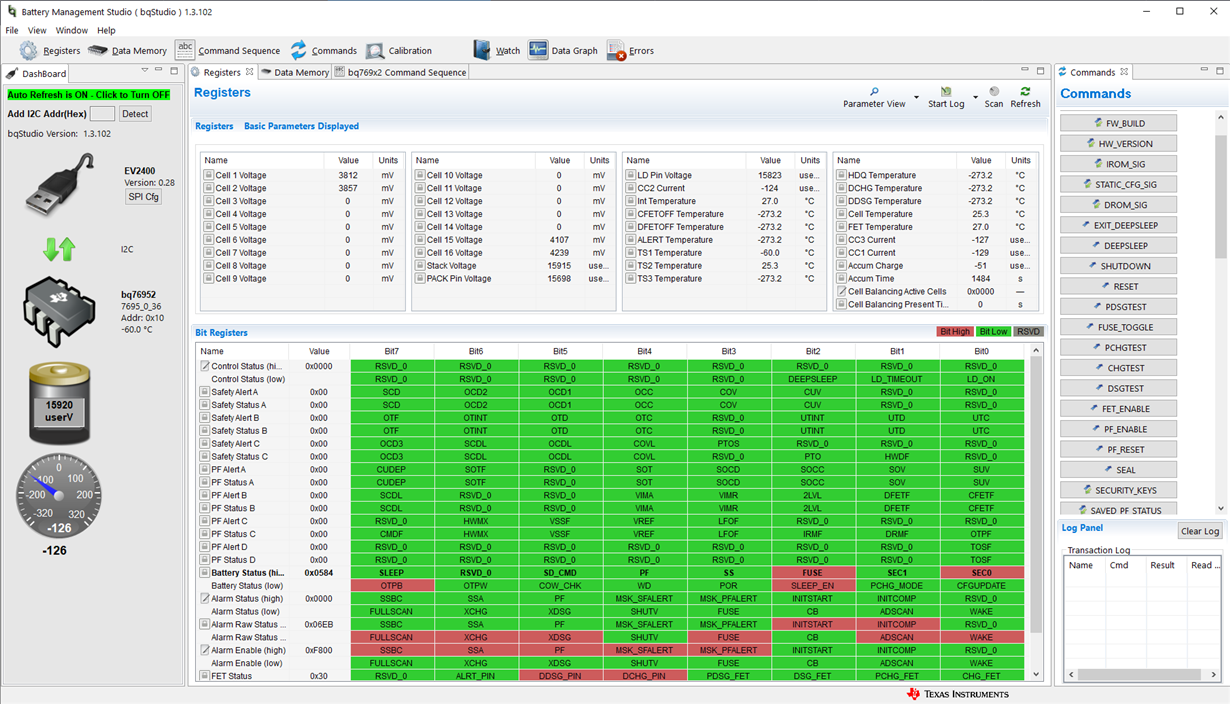

First I set the following registers for initialisation:

- I enter the Config Update mode,

- initalize the used cells in Vcell Mode: 4 cells at cell 0,7, 8, 9 (addr: 0x92EA -> data: 0b 0000 0011 1000 0001, LSByte first)

-> could be problematic as datasheet states that at least cell 0, 1 and 9 should be connected -> will be changed in next hardware revision - set the balancing config: do balancing when relax, sleep and while charging (addr: 0x931A -> data: 0b 0000 0111)

- set the DA config : use internal temperature for FET-temp and cell-temp and use milliamps and millivolts (addr: 0x92E9 -> data: 0b 0001 1001)

-> no external termistor is connected, when I read the DASTATUS5 later Cell- and FET- temperature is still at ~214K but Internal temp is ~310k - set the CB_SET_LVL to 3900 mV (addr: 0x0084 -> data: 3900, LSByte first)

-> this subCommand has some different behavour: when SubCmd is written to 0x3E, 0x3F and re-read it does say 0x00 0x00 (after 0xff 0xff) instead of the SubCmd - set the gain for current and capacity sensing

- exit the Config Update mode

- disable sleep mode

When I read the SubCmd CB_ACTIVE_CELL (0x0083) I always get 0xFF.

-> I dont really understand this SubCmd, data sheet say different things about the datasheet in page 92 ( Reports the actively balanced cell [-> maybe as index], Write 0xFF to turn

balancing off ) and page 68 (Bitmask of active cells .Write 0x0000 to turn balancing off.)

Writing of CB_ACTIVE_CELL (0x0083) doesn't change anything.

Edit on 24/09/2020 16:40: finishing the post