Hi,

I would like to double confirm 2 questions below.

1. Current design is with 2.5MHz Fsw for 12V to 1V conversion.

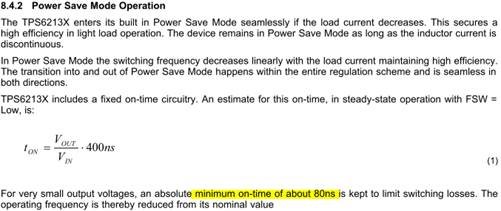

As datasheet mentioned, the minimum on time is 80nS, but we got 60nS, is it within the spec?

And it looks the Fsw is limited to 1.58MHz.

2. There is glitch at rising edge of phase, is it due to miller effect?

Thanks and Best regards,

Tiger