Hello team,

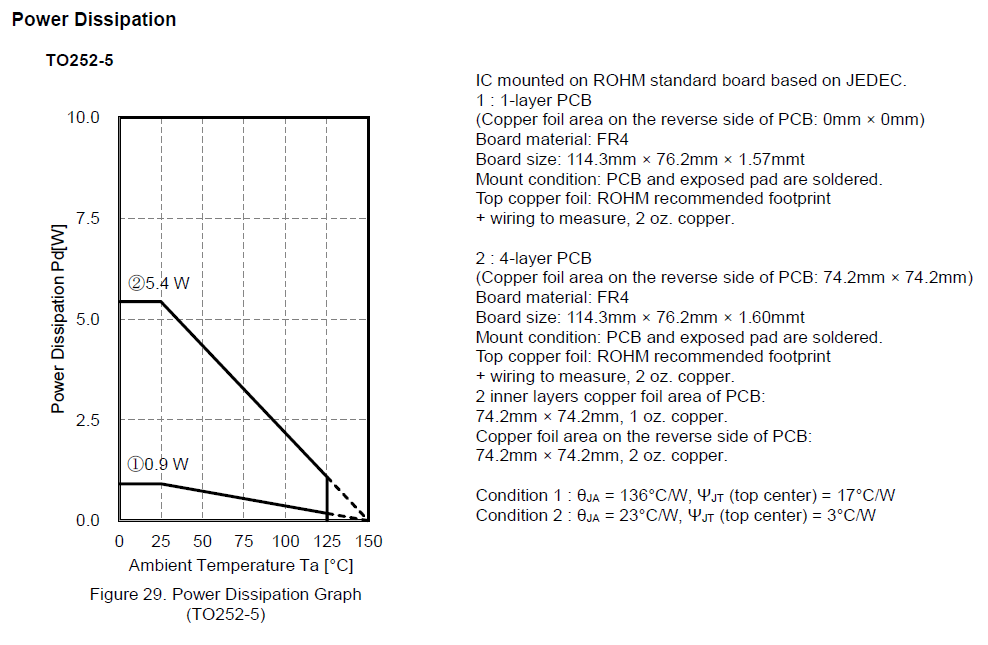

My customer wanted to get some information about Power dissipation as the below picture that is a device of other company.

Is there any experimental data about PD of TPS7B86-Q1 not a simple PD calculator?

Thank you.

Best Regards,

Kevin Shin