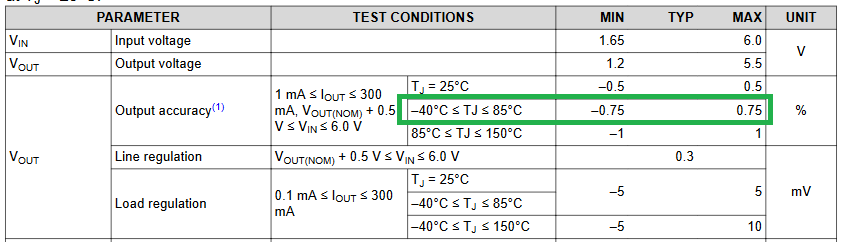

TPS784's datasheet shows a good accuracy number of 0.5% on page 6, and 1.5% on page 21. I noticed that CircuitEXP lately demonstated that TPS784 can only achieve a 5% output accuracy per their online tutorial.

It seems that, to achieve 3% accuracy, the resistance needs to be much lower for TPS784 due to the bias current variation. Could you please confirm the analysis result shown in table 8-1 in the datasheet?