SMBus 2.0 specification

SMBus 2.0 specification: http://smbus.org/specs/smbus20.pdf

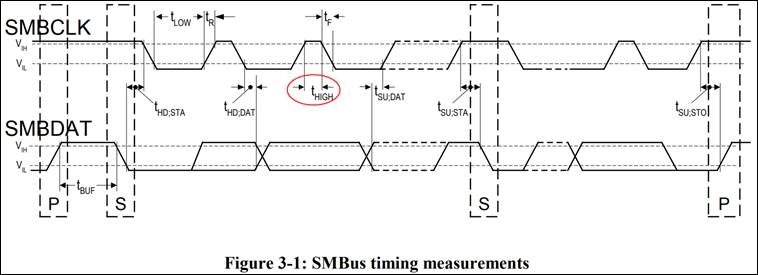

The following figure is taken from the SMBus 2.0 specification, Page 11, Figure 3-1: SMBus timing measurements The following figure is taken from the SMBus 2.0 specification, Page 13, Figure 3-2: Timeout measurement intervals

The following figure is taken from the SMBus 2.0 specification, Page 13, Figure 3-2: Timeout measurement intervals

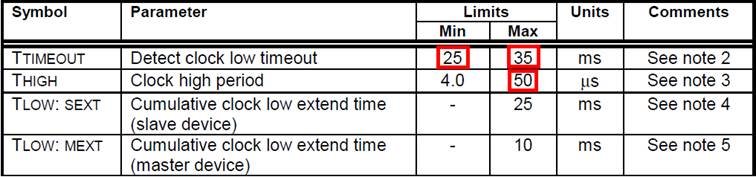

The following table is extracted from the SMBus 2.0 specification, Page 11, Table 1: SMBus AC specifications

UCD31xx Digital Power Supply Controller - PMBus Interface/I2C Interface

File Title: UCD31xx Digital Power Supply Controller, Literature Number: SNIU028D FEBRUARY 2016 – REVISED SEPTEMBER 2020

File URL: https://www.ti.com/lit/ug/sniu028d/sniu028d.pdf

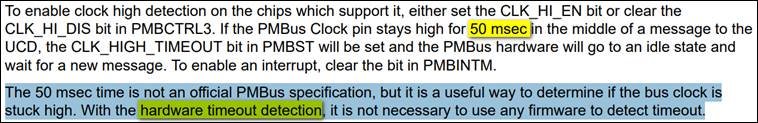

The picture below is a screenshot from the description of the file content (Page. 386), Clock High Timeout Detection

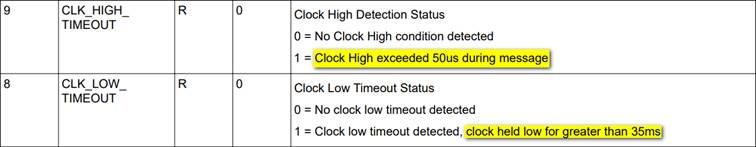

The following figure is a screenshot from the description of the file content (Page. 419), Table 10-7. PMBus Status Register (PMBST) Register Field Descriptions (continued)

Question

Hello Experts,

- Does the function of CLK_LOW_TIMEOUT correspond to the TTIMEOUT specification in the SMBus 2.0 specification?

And please explain CLK_LOW_TIMEOUT detection working principle. - TLOW:SEXT, and TLOW:MEXT in the SMBus 2.0 specification. Is there any corresponding function support in the UCD3138?

And please explain detection working principle. - In the document file, (Page. 386) and (Page. 419), why are the units of Clock High Timeout Detection different?

Thank you very much for your reading and answer.