Dear all,

I am doing a project with the requirement configuration stated below.

| Configuration | |

| Label | Value |

| VIN | 15V |

| VOUT | 1.2V |

| OUTPUT CURRENT |

1.5A |

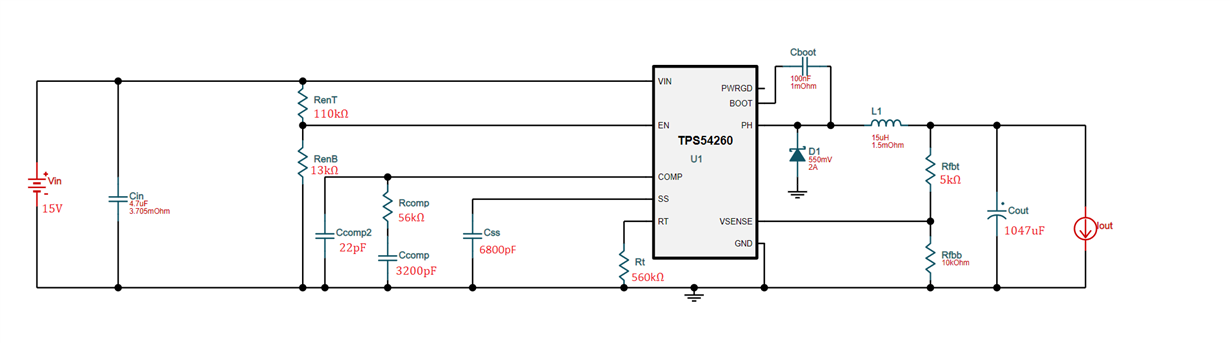

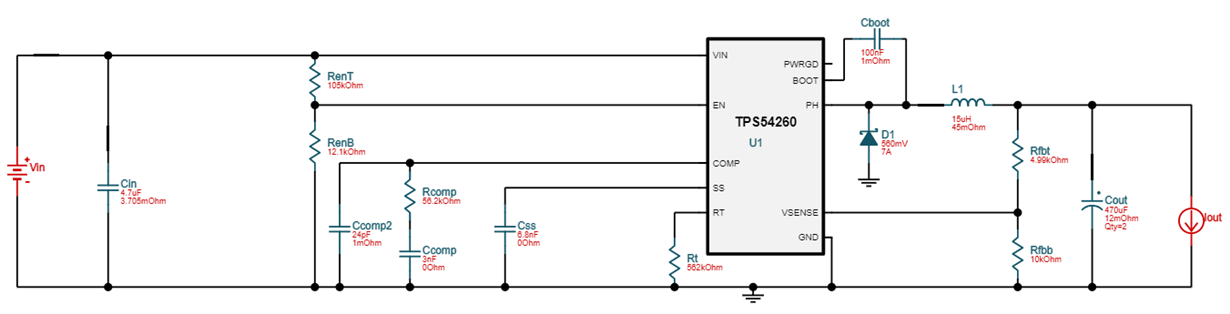

I use TINA simulation tool to determine the components value. Based on that, I had made some changes to the components value that is label in the schematic below with the reference from webench power designer. Then I am using TPS54260EVM-597 evaluation module (HPA597)

However, when testing the circuit, I encounter critical issue listed below:

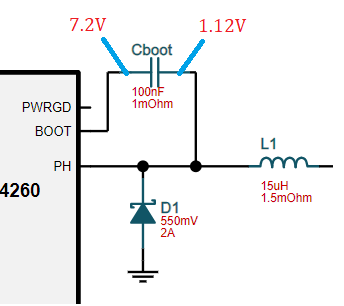

1: Input of Cboot voltage is 7.2V and the Output of Cboot voltage is 1.12V

2: Results for switching frequency measured before the inductor is not working

Please assist where the root cause is, Your prompt reply is appreciated.