Other Parts Discussed in Thread: UCC21732

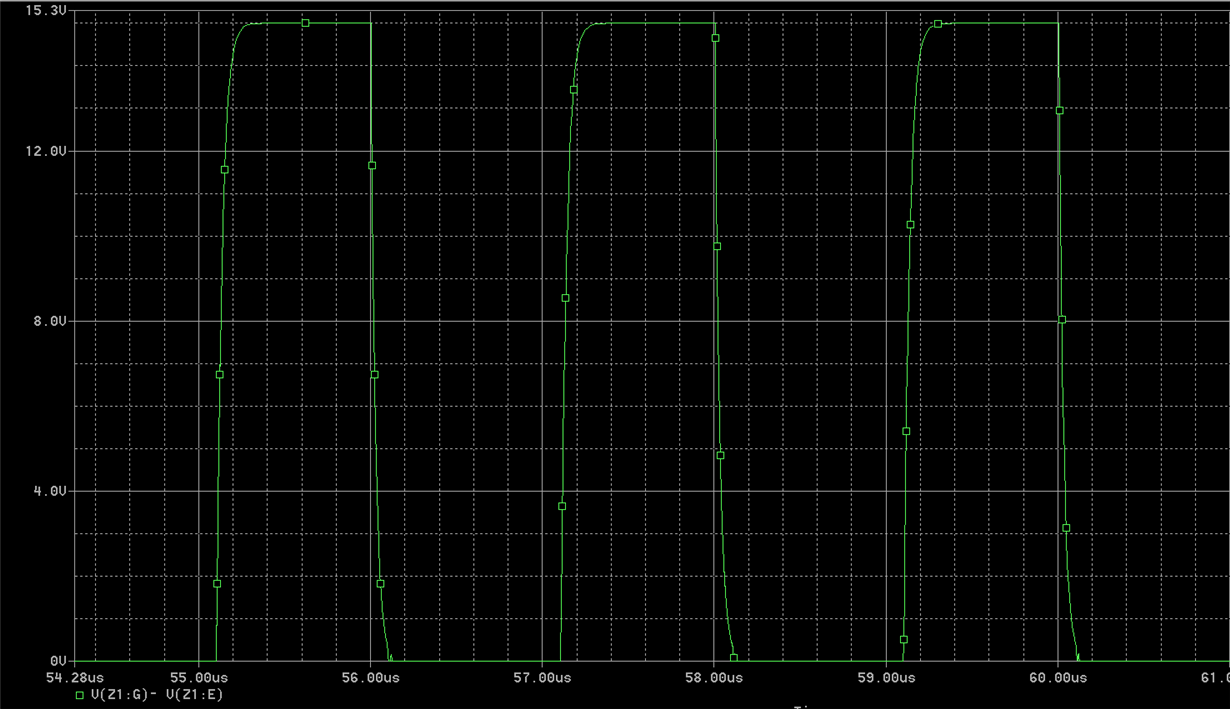

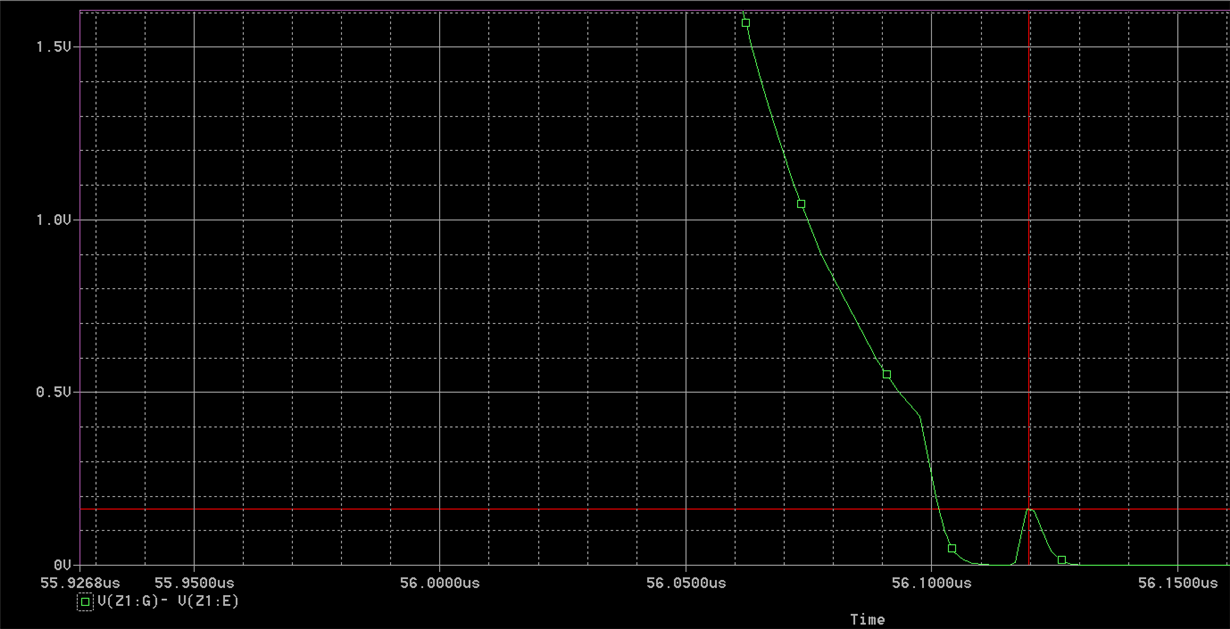

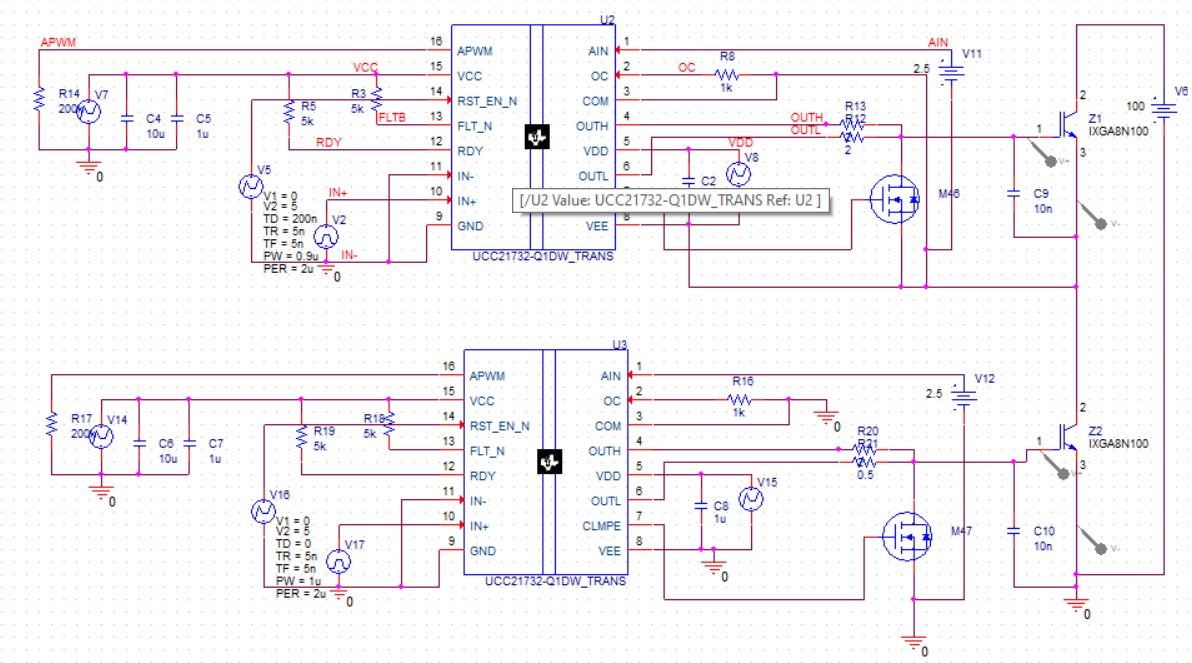

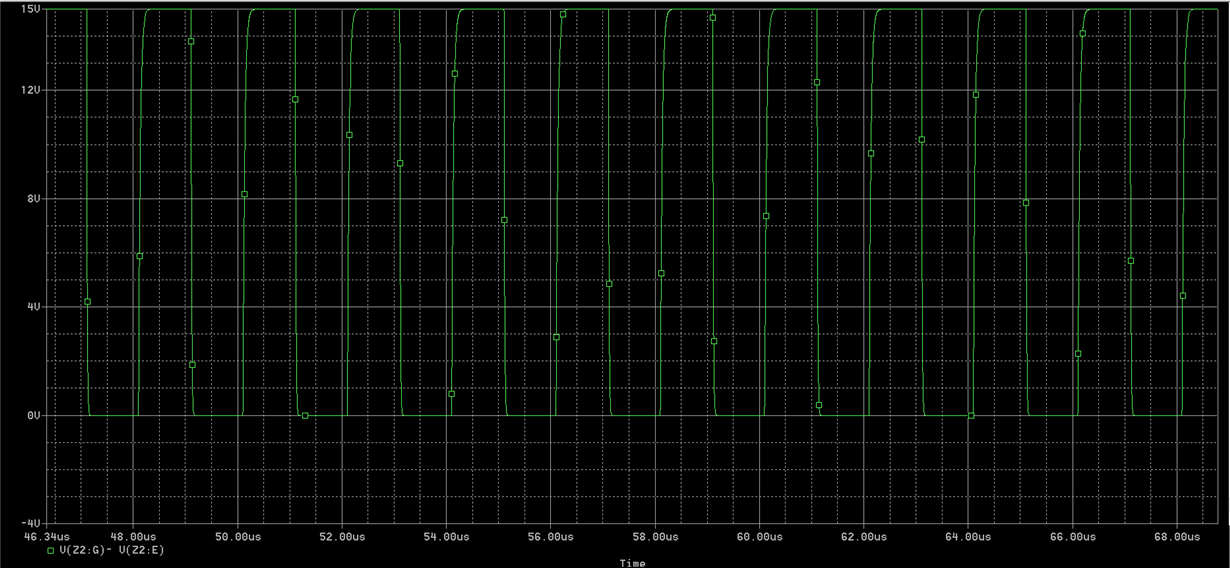

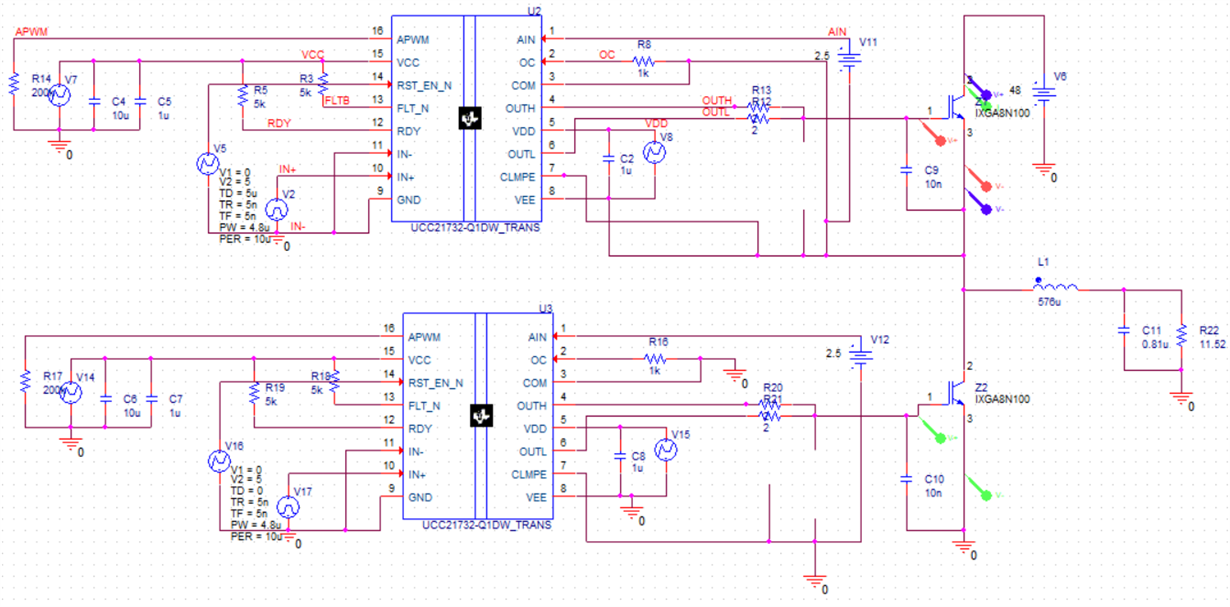

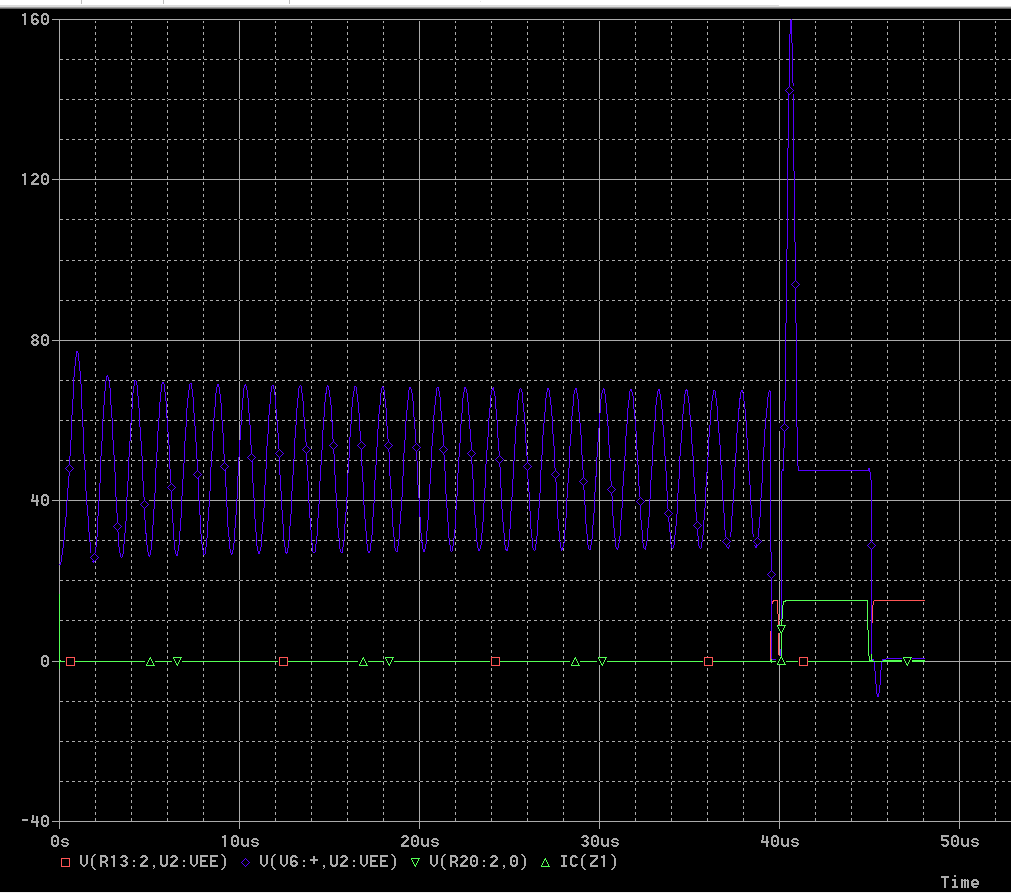

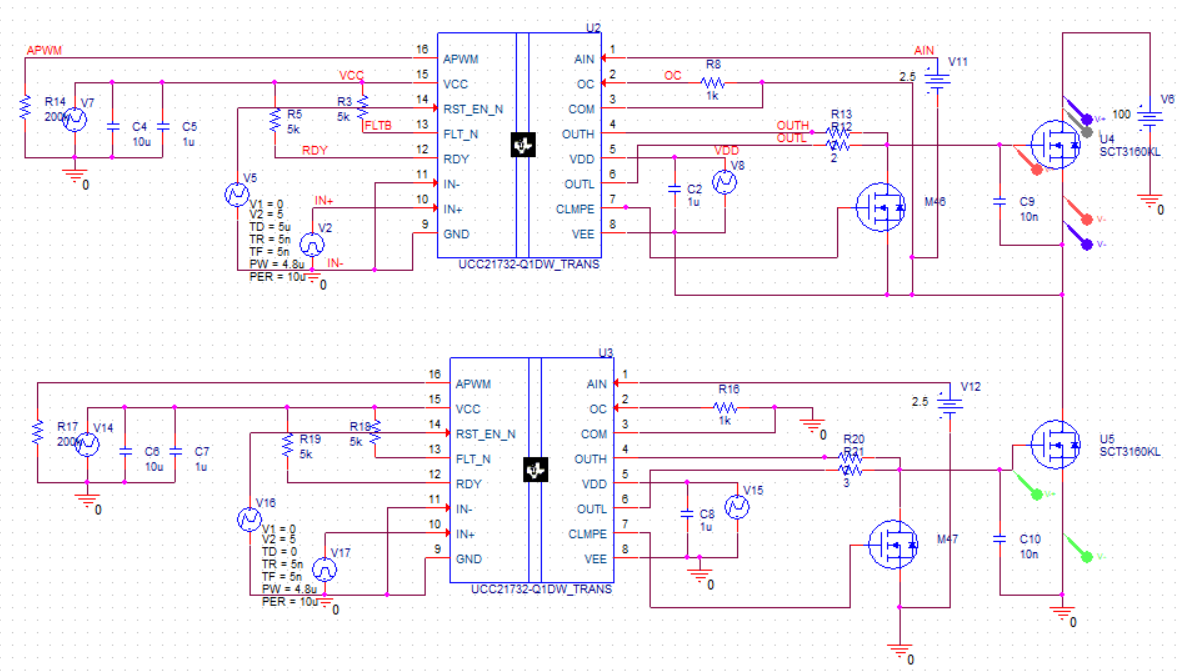

I am trying to study the effects of dv/dt on SiC MOSFET false turn-on. I am using UCC21732 gate driver IC from TI. Initially I am simulating using the downloaded files from TI website, which has an IGBT in place of MOSFET. My problem is that when I simulate it for DC Bus voltage = 100 V at switching frequency on 500kHz, (a higher DC bus like 500 V does not converge in Pspice sim) I am getting a few millivolts glitch in the top device, but no glitch at all in the lower device. This is happening for both with active clamp MOSFET and without it. I tried to go from 10V to 50V to 100V but I don't get anything with any value of OUTH and OUTL resistors for the lower device. Here is my circuit and waveform:-