Hi

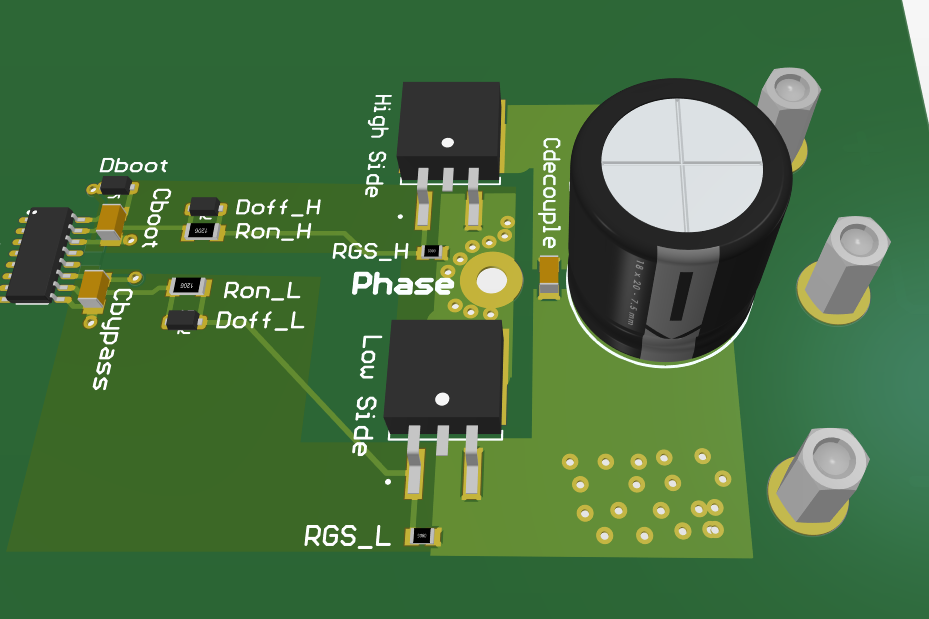

I am trying to design a half bridge for motor driver 36v-48v , based on what i read in several appnotes like " Best Practices for Board Layout of Motor Drivers".

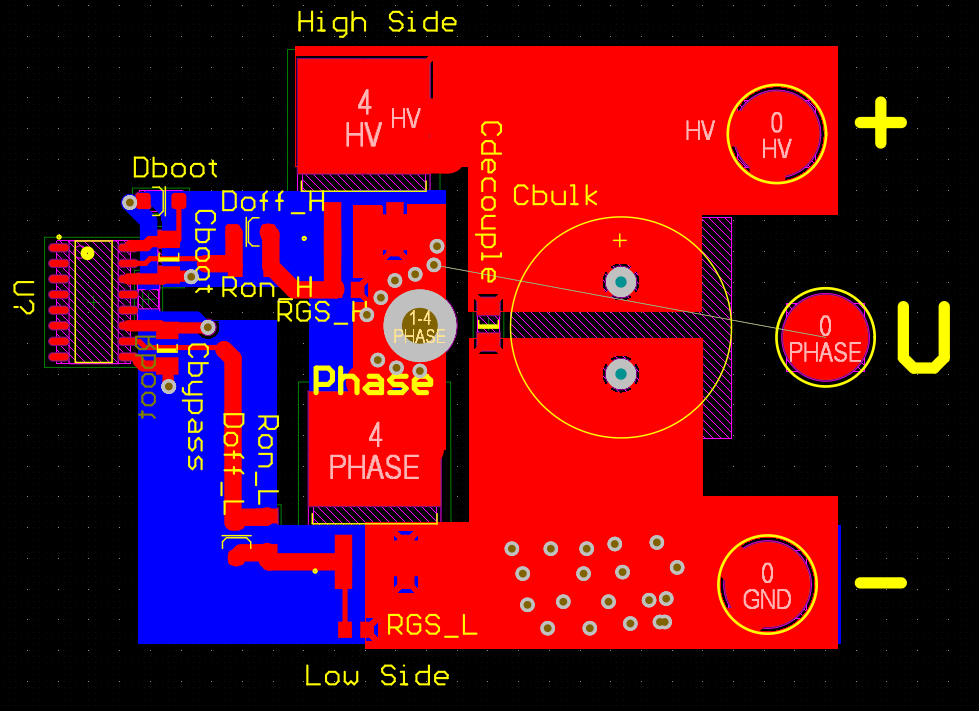

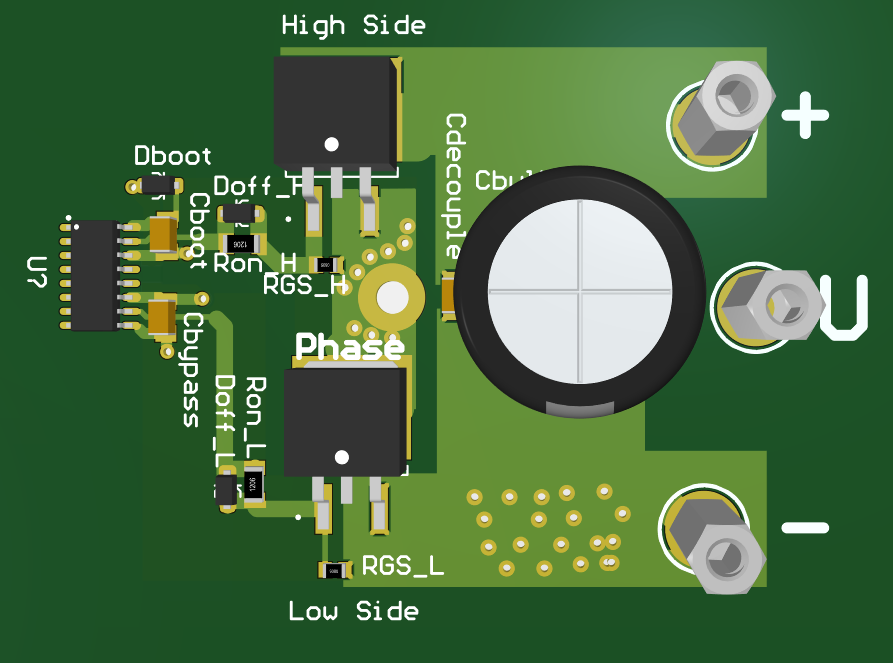

I have drawn this simple circuit and i want to know if the layout applies the rules to minimize inductance and reduce switch node ringing:

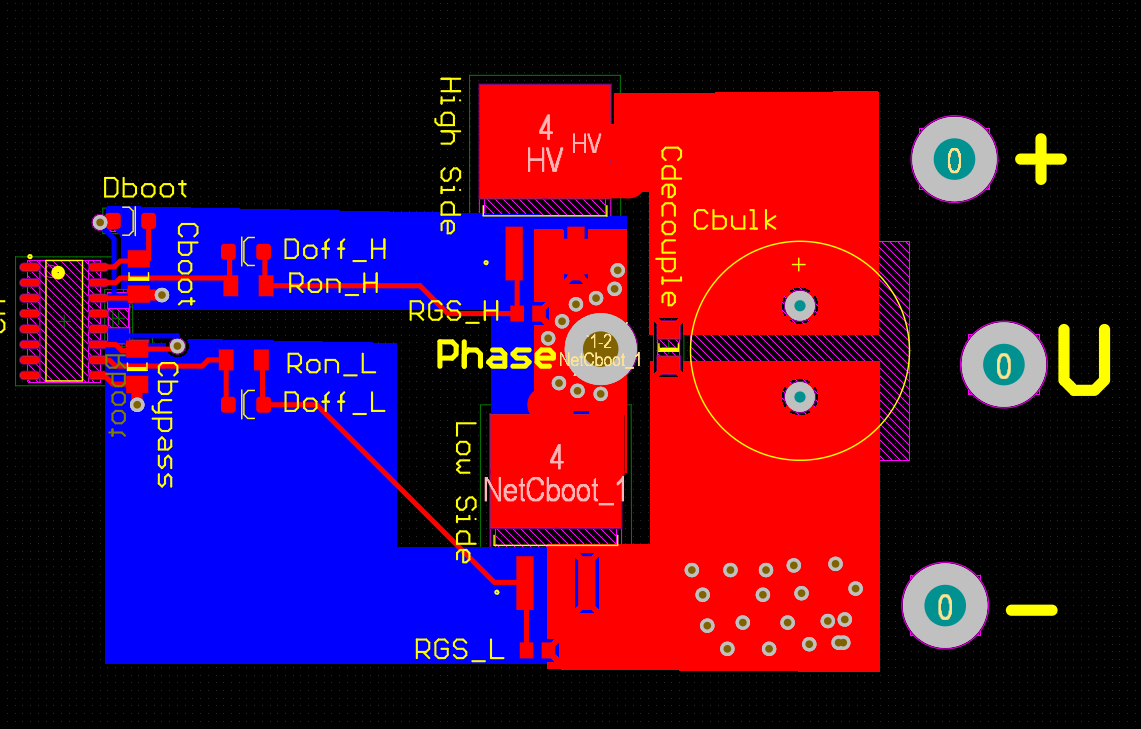

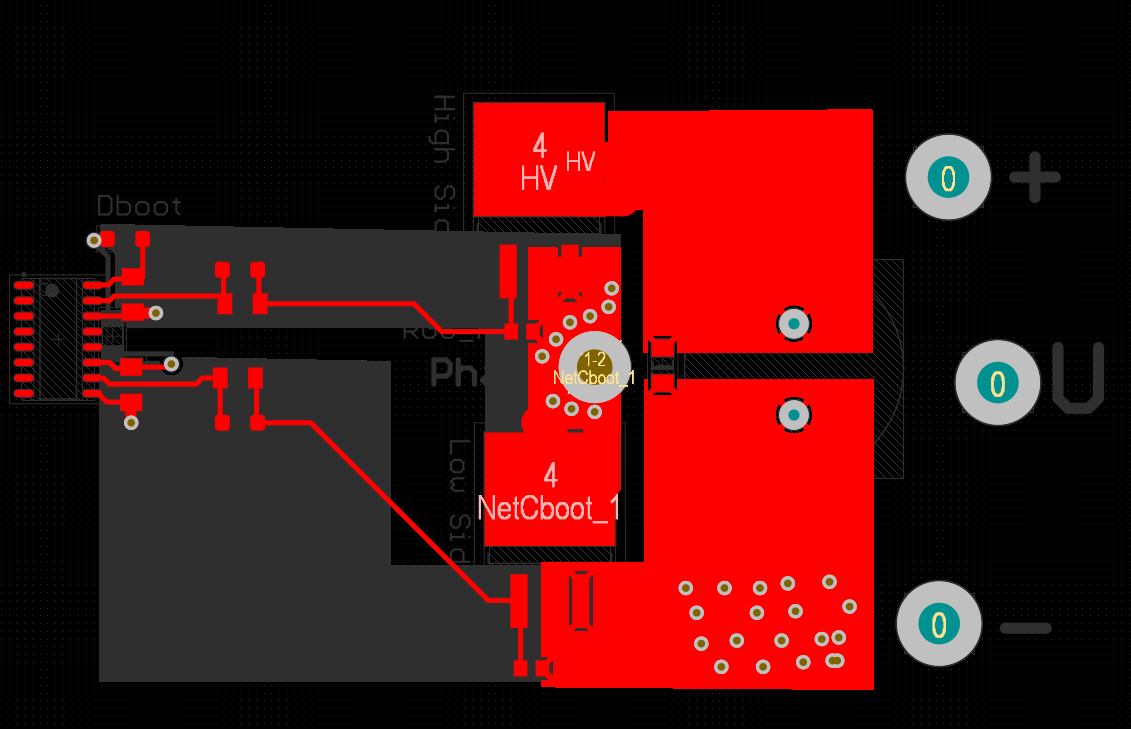

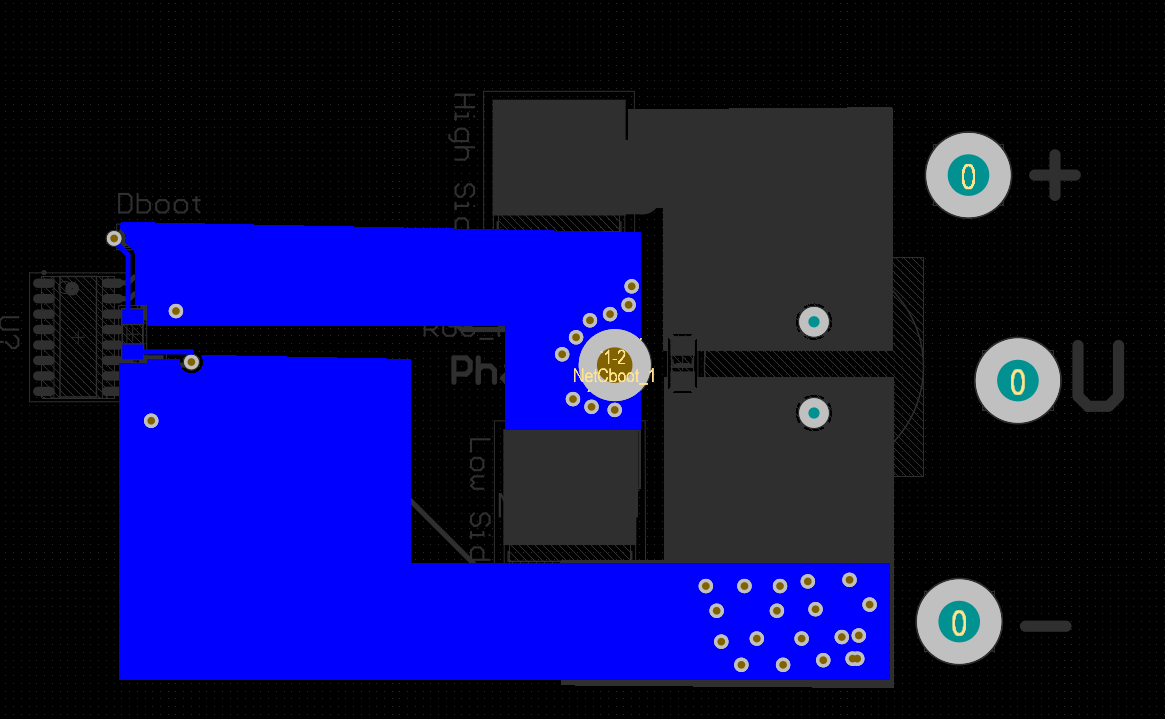

1. Each gate signal has the the return path (reference plane) under neath in the bottom layer.

2. switch node (denoted here as phase) doesn't cross the power HV and GND planes and doesnot come close to Low side gate signals.

Question : Which is better , using a wire to connect point Phase to the standoff "U" externally , or using a 4-layer board and connecting these 2 points using internal plane ?

Any other suggestion regarding making the layout better?

note: this is an example only to grasp the idea, the real circuit will have 3 mosfets in parallel , and it will be more tight ( the gate driver will be closer to the mosfets)