Hello TI Team,

Myself Meghanath,

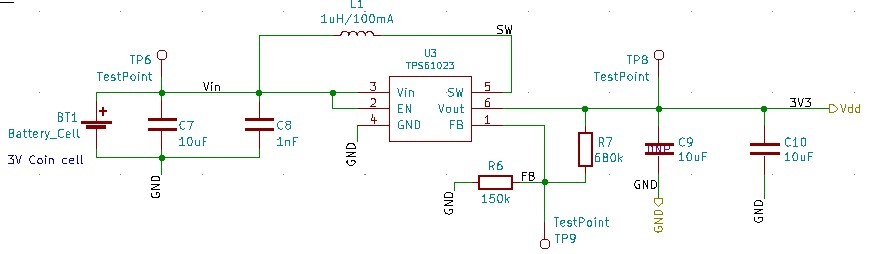

I'm using a TPS61023DRLR a Boost Converter IC in my design for the o/p voltage of 3.3V with a current of 50mA having input voltage of 3V from a coin cell battery.

I'm facing a following issues:

1) As soon we power up the HW, the o/p voltage dipping to 2.6V, FB voltage is dipping to 0.45V and SW- GND are shorted.

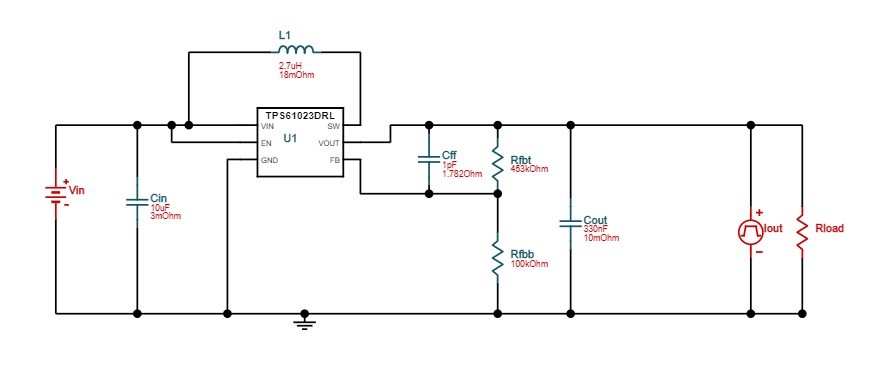

2) Then we built a Boost circuit in breakout board for the above mentioned values and tested,

I) When we test without Load, the o/p voltage is 3.3V. FB voltage also coming fine (0.6V) which is typical.

II) But when we connect a load of 330 ohm(10mA) , the o/p voltage is dipping to 2.6V. FB voltage also dipping to 0.45V.

III) Same Scenario is observed with the different loads - 150 ohm (22mA), 100 ohm (33mA).

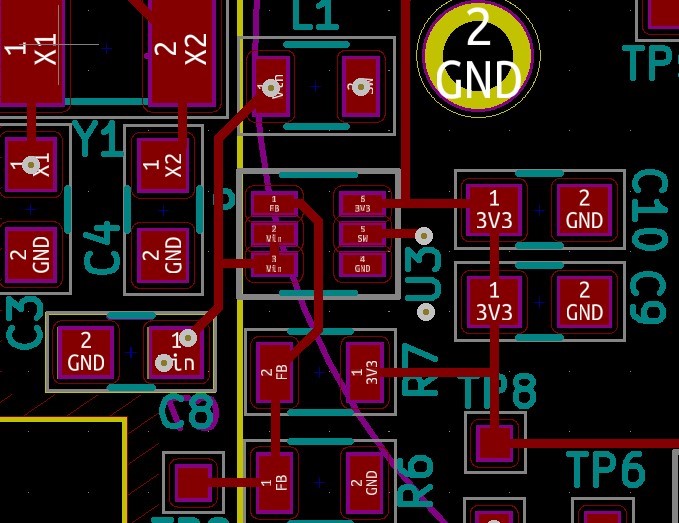

Below attached image is the designed circuit.

Output capacitors changed to two "22uF".

Please suggest a solution for the above issue.

Thank you.