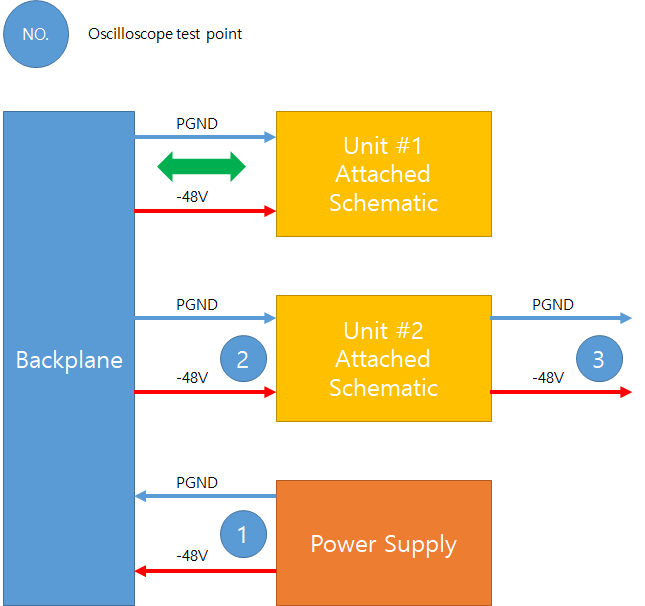

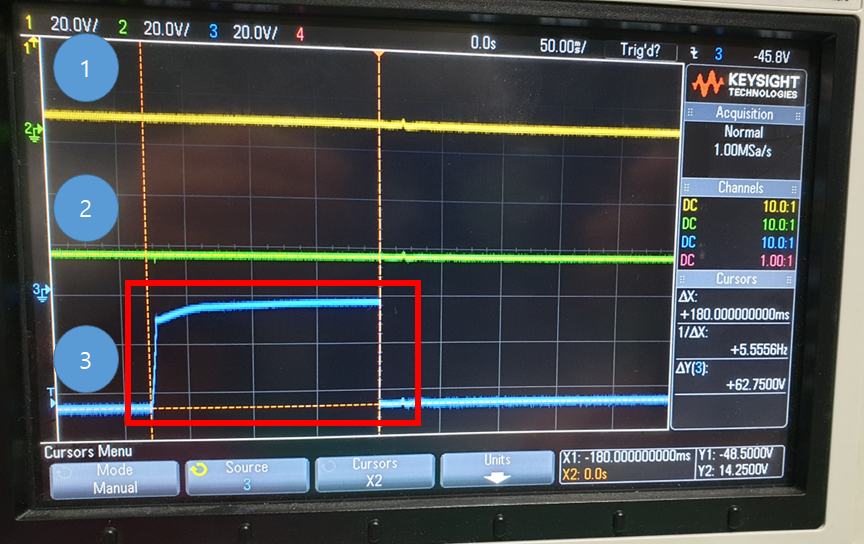

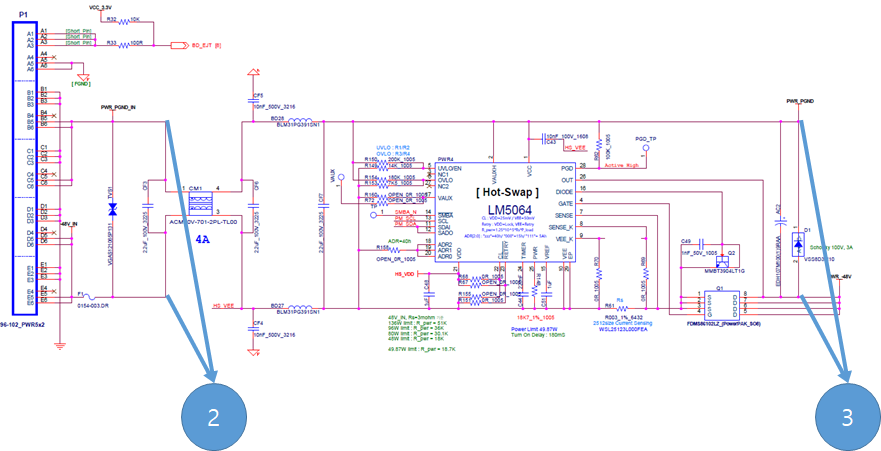

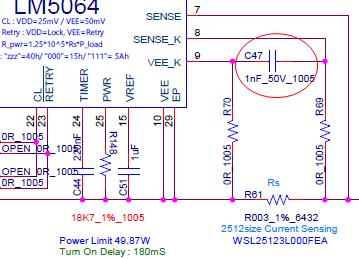

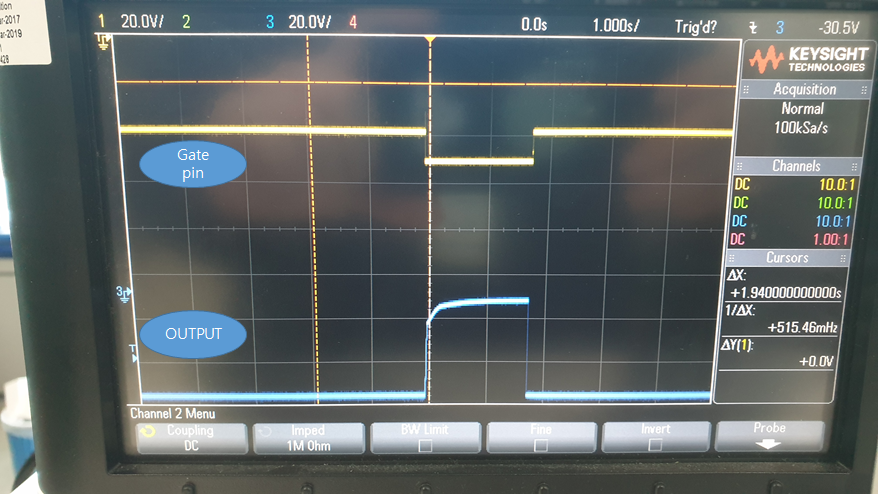

The system is configured as shown in the attached picture. If Unit #1 is inserted while Unit #2 is inserted, it seems that Unit #2's hot-swap (LM5064) is in progress. -Oscilloscope point 3 (actually reset.)

When the power supply and the input power of Unit #2 are checked by scope, there seems to be no problem at all. I have no idea for any reason.

The above phenomenon is also the same in the opposite case.

(For example, when Unit #1 is inserted while Unit #2 is inserted)

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.