Hi

The customer use two BQ76930 cascades to design 20 series of iron-lithium protection boards.

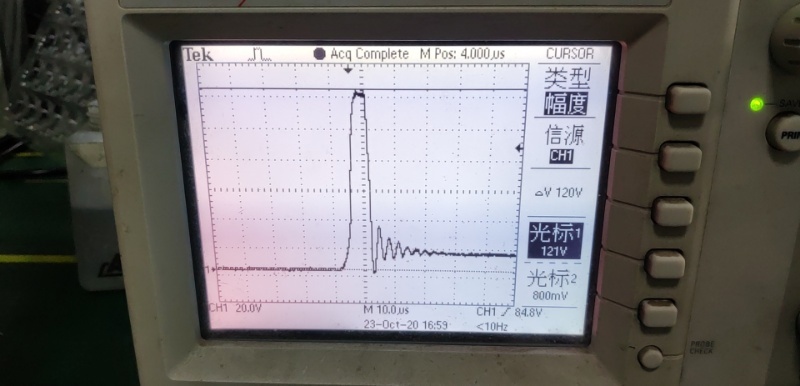

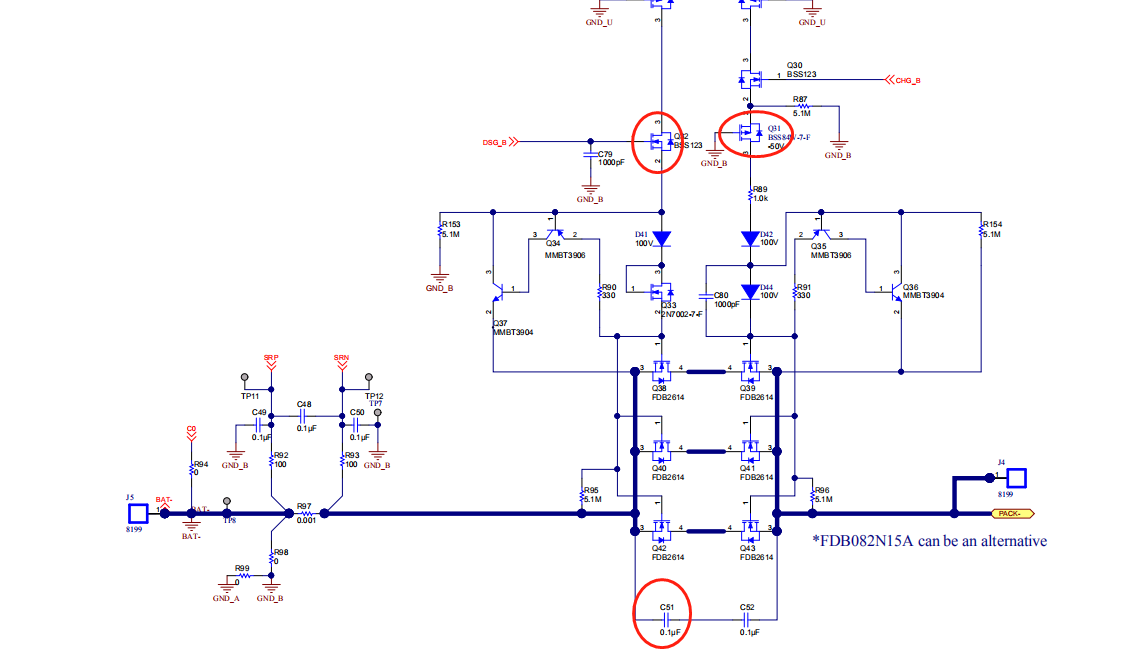

During the short circuit test, it is found that there is an instantaneous high voltage between the DMOS, the voltage is about 120V, and delay time is 7.2uS, the capacitor C37 (marked) damage and other components, as shown in the figure.

(Trying to add a 90V TVS tube between B+/B- and adding a Schottky diode between B-/P- is invalid)

The attached figure mark the component is easy to damage. the failure rate about 0.5~1%

Please give some suggestions.

Thank you

Star