Other Parts Discussed in Thread: AM3358, , PCA9306

Hi,

We are using BQ24725ARG on our PCA, and AM3358 communicates with BQ24725ARG through I2C (SMbus).

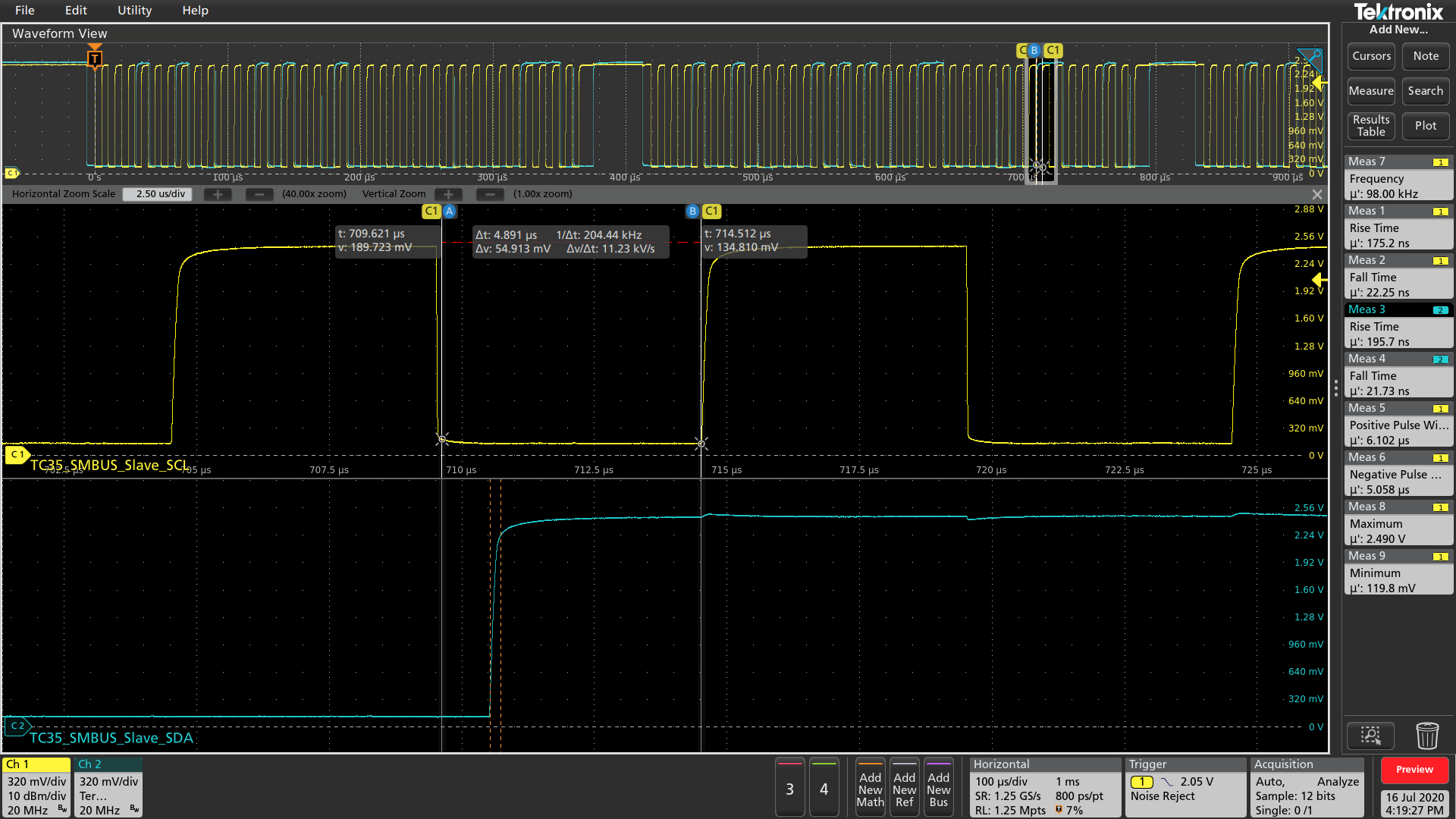

We noticed that sparsely in Charge Options Register reading transaction BQ24725ARG pulls SCL (SM_CLK) low for more than 40ms before releasing SCL for next I2C communication . This 40ms is longer than the SMbus maximum Timeout value which is 35ms defined in the SMbus specification.

The question is why BQ24725ARG pulls SCL low for such a long time?

When BQ24725ARG pulls SCL low for such long, what should the I2C master (AM3358) do for next reliability I2C transaction?

The oscilloscope waveform is attached at the end of this post for your reference.

Thanks,

Peng,