Other Parts Discussed in Thread: LMG1205, LMG1210

Hello TI

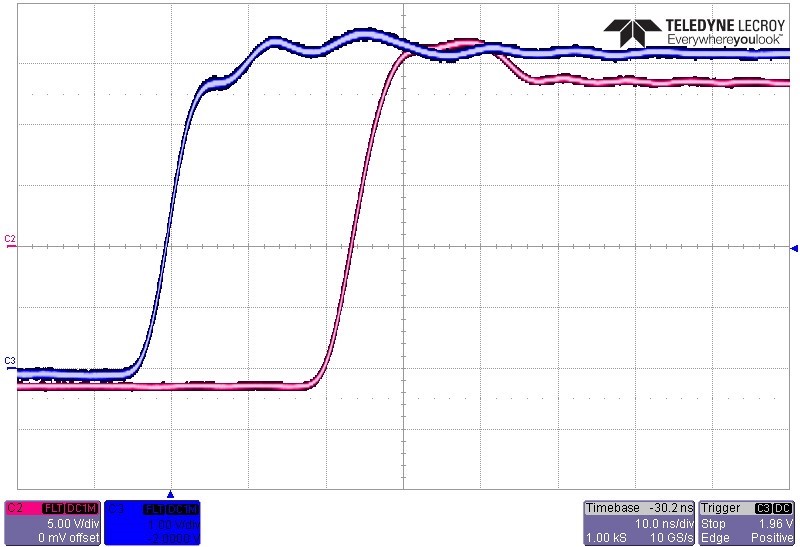

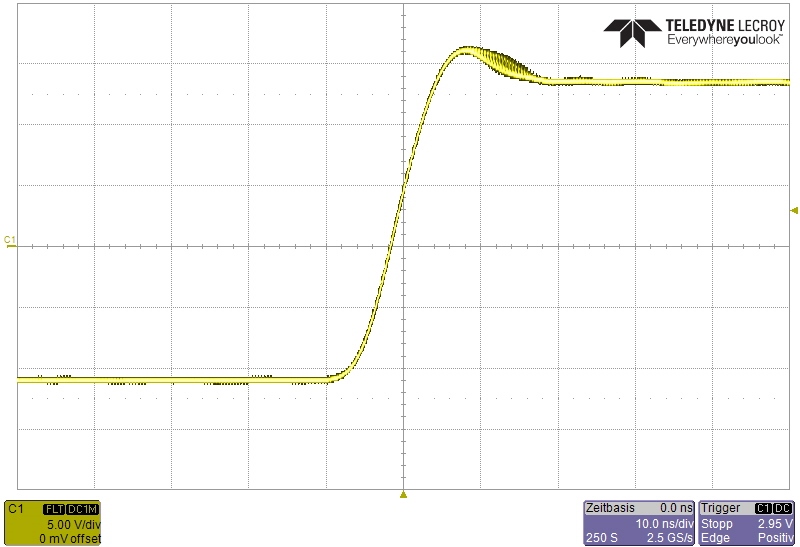

We have an application (H-bridge step-down converter) where an absolute low-noise operation is required. We noticed variations in the output voltage, which we could trace to a Jitter in the phase-leg-output voltage waveform, as shown in the picture below (first division after t=0, recorded with persistency)

This (sometimes) happens, when a negative phase-leg output current commutates from the lower FET to the upper diode, and then after the deadtime to the upper FET.

Note that the slow slope is due to the limited bandwidth (100 MHz) of our differential probe.

This jittering does only happen in a certain range of operation points. Funnily, it disappears if we connect an other differential probe to the PWM input signal of the LMG5200.

Any idea why this could happen?

Best regards

Beat Ronner