Other Parts Discussed in Thread: BQ40Z50

Hi TI Team,

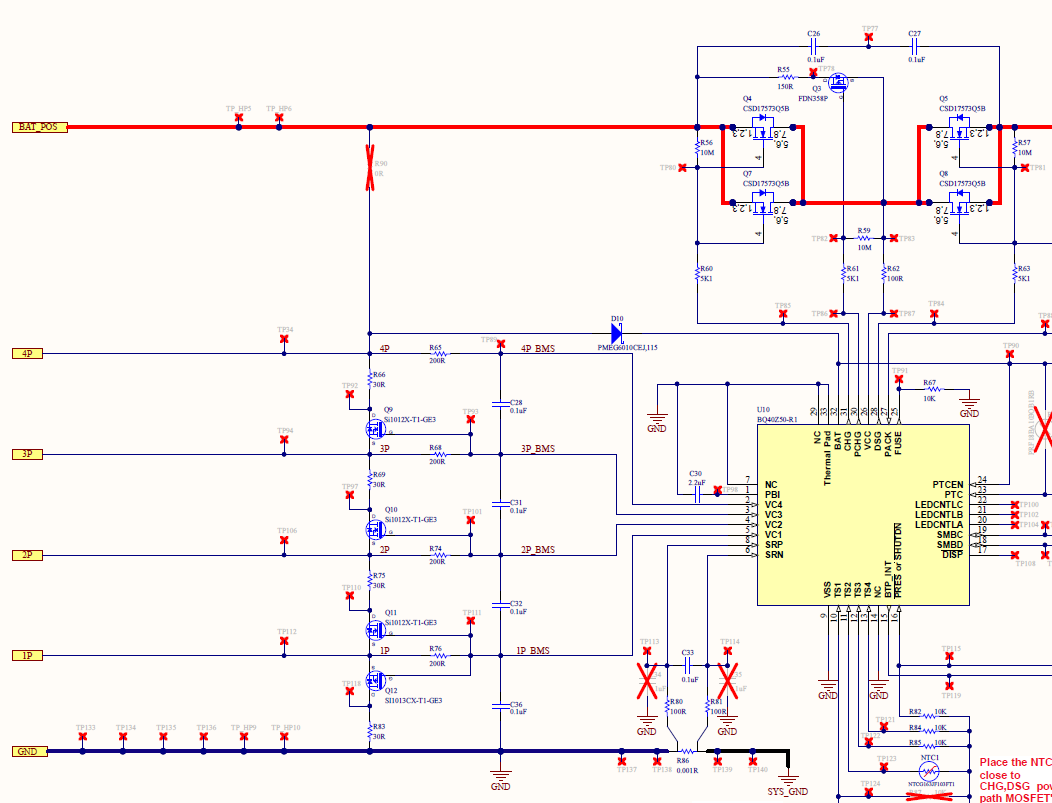

We are using the bq40z50 in our LiFePO4 4S pack design and encountering odd failures on some assembled BMS PCBs.

In order to make the voltage measurements of the top cell more accurate as needed with LiFePO4 cells, we split the positive high current path from the top cell balance/sense wire.

This means that the bq40z50 BAT pin is fed only by the sense wire and the bq40z50 VCC pin is fed by the positive high current wire.

Our cell stack exposes 2 high current wires B+ and B- and also a four pin balance/sense connector.

Do we need to connect the BMS PCB in a certain order to the wires from the cell stack?

Does the VCC pin (fed by the high current wire) need to see a valid voltage before the BAT pin (fed by the sense wire) so the bq40z50 will not see an invalid voltage difference between it's two power domains?

Best regards,

Shahar