Hi,

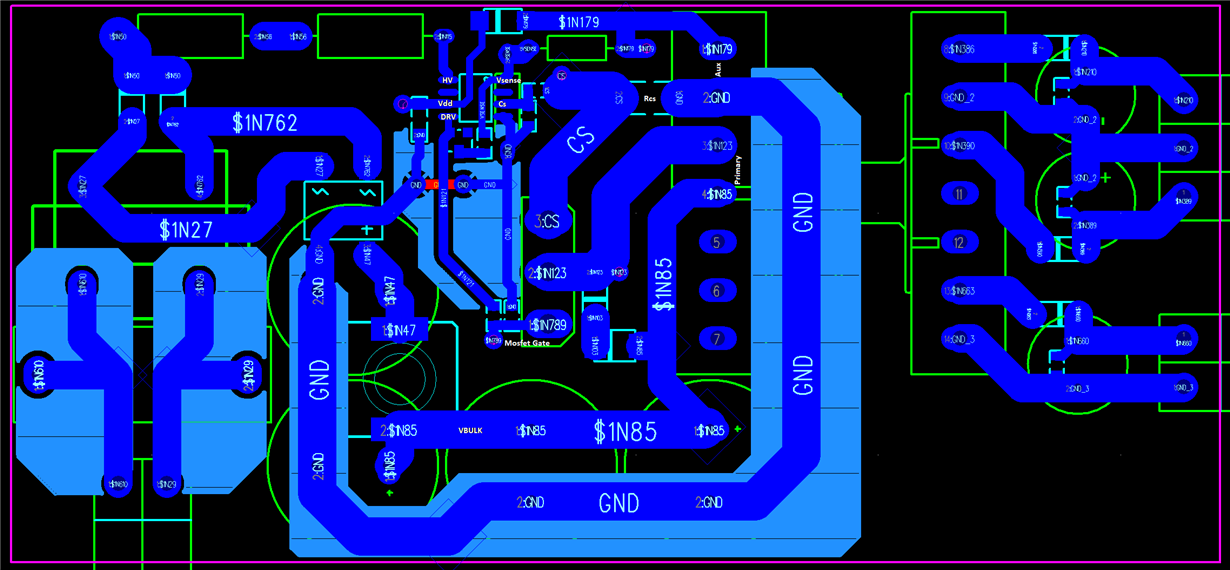

I have designed a basic circuit based on webench and spreadsheet calculator.

My circuit and some wafeworms are as follows.

I have followed the datasheet and spreadsheet. Only difference is I knew the current sense resistor was 0.2 ohms before I got the waveforms and I realized it is 0.22 ohms while I was preparing this message.

The output is designed for 19.5V/~60W

As you can see from the waveforms it does not start-up and latches-up.

The current waveform is weird I think. I tried to be careful for pcb layout. I don't know why is it like that and I don't know if it is the origin of theproblem.

If I change the mosfet with a 2A/1500V one with a gate resistor of 15ohms, the latch-up goes away but it restarts forever in that case. If I change the gate resistor to 5.1 ohms then latch-up occurs again but the current waveform is significantly less oscillatory.

I have also added the spreadsheet file that I use.

5037.FLYBACK TRANSFORMER DESIGN TOOL.XLS

Hope I can get a help here, because I am clueless and don't know what to do.

Thanks.