Hi expert,

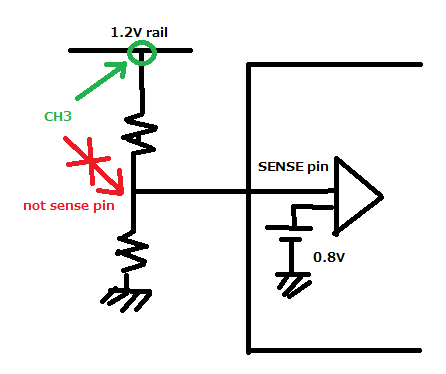

My customer plan to use TPS3870J4080DSERQ1 (0.8V) with latch mode(CT=0V).

They plan to input pulse to CT pin for unlatch.

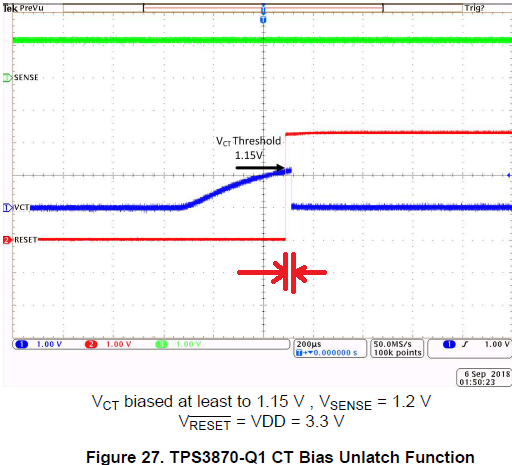

If they will input over 1.15V voltage continually to CT pin, how does the Reset output work at this timing? (at Sense pin > 0.8V)

In case of the following waveform (datasheet Figure27)

Why will the reset pin be High-Z after unlatch?

I think, The reset output will be low after unlatch, because Sense pin=1.2V (= OV condition).

Thanks

Muk