Hi,

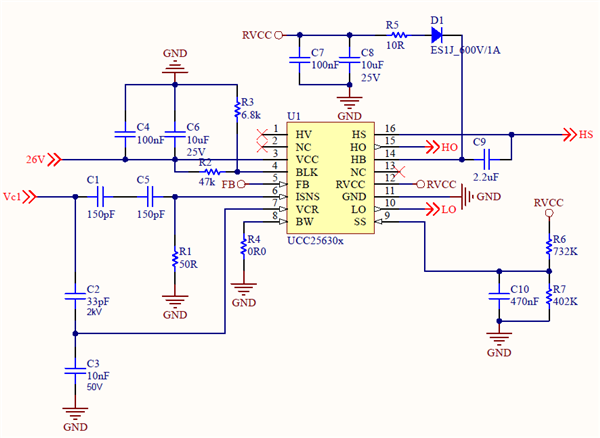

I'm testing this device under no-load conditions with the schematic diagram shown below.

Other setups in Fig. 1 are:

- VCC is supplied externally.

- Vin UVP/ OVP is not used so BLK is tied to VCC thru a volt divider, which results in 3.3V at BLK.

- Vo UVP/ OVP is also not used so BW is short to ground.

- The LL/SS resistors and BLK voltage set the burst mode threshold (VLL) around 0.9V.

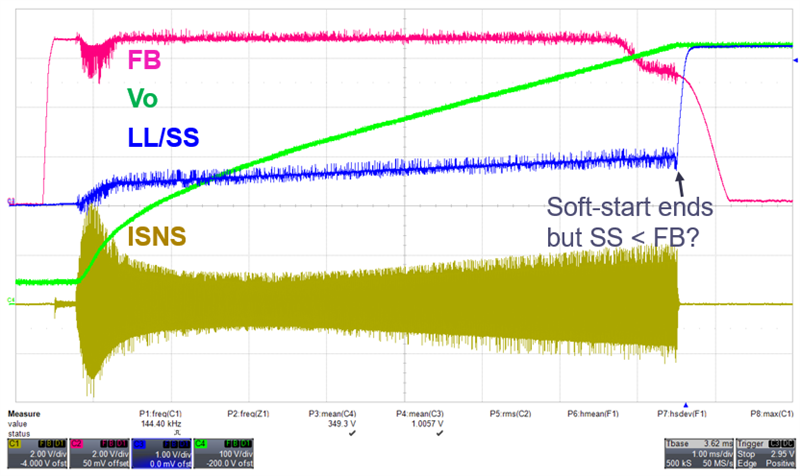

From the startup, the gate starts switching as expected, although the termination of soft-start seems a bit early.

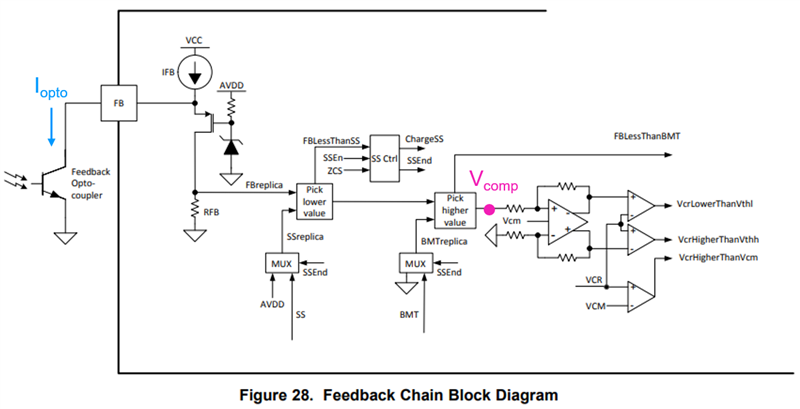

The condition of soft-start termination should be SS > FB.

However, according to Fig. 2, SS goes to BLK (3.3V), which indicates the end of soft-start, but FB is still around 5V.

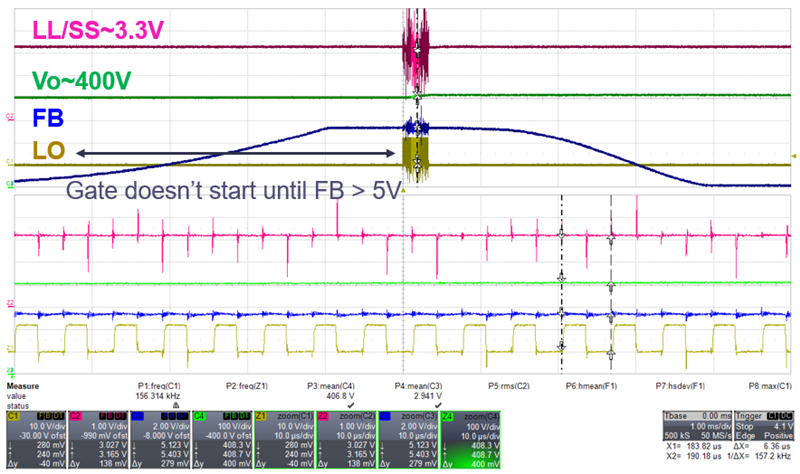

And then it enters burst mode as there is no load at the output:

As Fig. 3 shows, in burst mode, FB ramps up from zero but there is no gating signal until FB> 5V.

The optocoupler may experience saturation but LO does not start when FB > VLL (0.9V).

I also ever tried to open the feedback loop and supply FB externally. LO starts when FB > ~5V and stops when FB is less than the same voltage,

which is aligned with the closed-loop test results but not desirable. So I'm wondering what is wrong with the configuration.

In summary, I'm wondering why

1). LO stops before FB drops below SS at the end of soft-start?

2). LO doesn't start switching when FB> VLL in bust mode?

Regards,

Daniel