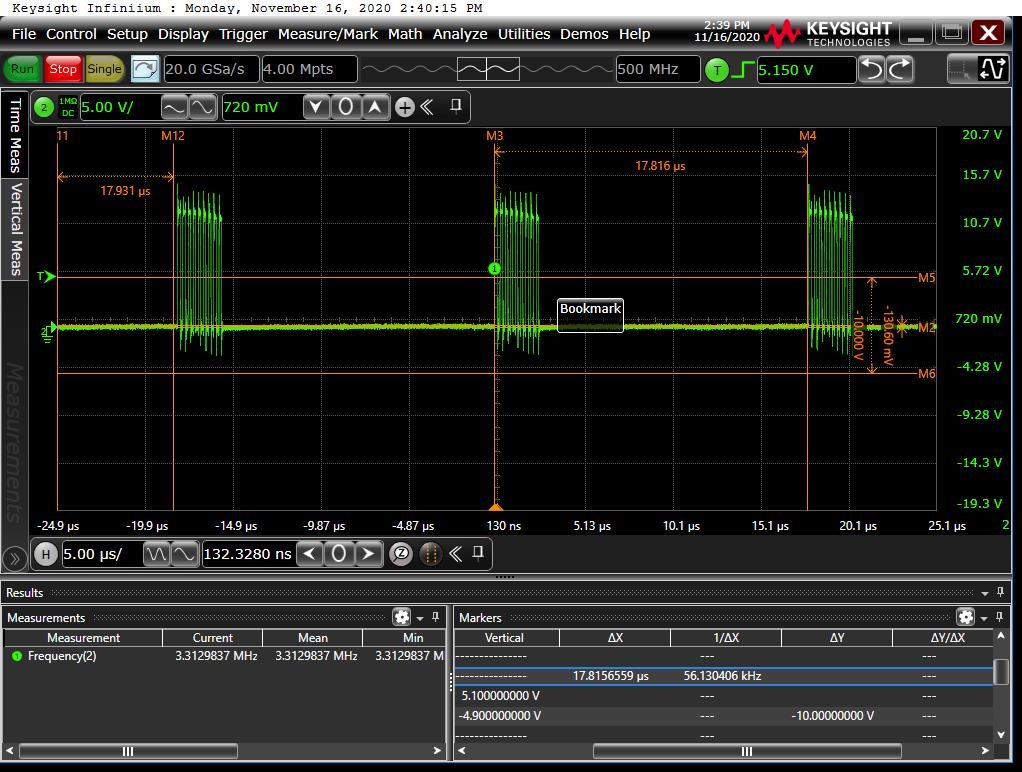

the Vout is not a fixed value, it has a 56KHZ 150+mV ripple。like as this:

I found this ripple signal follow the PWM signal, the PWM signal is not a continued singal,it is about 56KHZ on and off。that cause the VOUT have 56KHZ 150mv ripple.

So,why the PWM signal is 56KHZ frequency ON/OFF?