Hi,

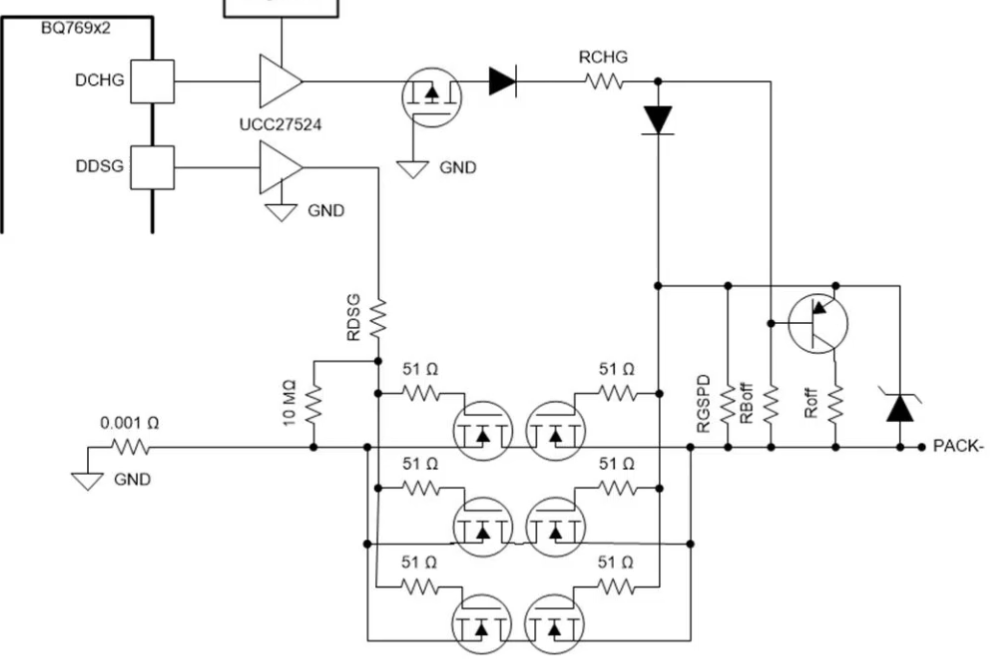

I am following below recommendation for low-side FET Drive:

And I have following doubts:

1. Is it okay to use a PNP BJT like BC856A-T?

As its had Emitter Base Voltage of 5V, but drivers are providing 12V for FET drive.

2. What should be specs of zener diode connected at output end, in terms of reverse breakdown voltage?

3. What should be considerations for choosing P-ch FET connected at DCHG Driver output?

Regards,

Anurag